| Spartan-3A VQG100 搭載ブレッドボード XCM-304 |

2009/01/10-

Spartan-3Aの評価や試作にご活用いただけます。

XCM-304-200Aは、販売を終了いたしました。受注生産をご希望の方はお問合せください。

XCM-304-200Aは、販売を終了いたしました。受注生産をご希望の方はお問合せください。| Extended Spartan-3A | |||||||||||||||||||||

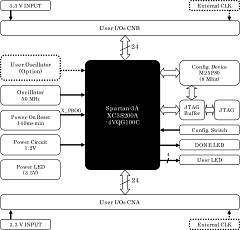

クリックして拡大 ブロック図  クリックして拡大 |

■ XC3S200A-4VQG100Cを搭載 ■ 48本のIOピン(4本はLED兼用)と6本の入力ピンを外部接続 ■ 汎用LEDを4個(外部引き出しIOピンと兼用) ■ コンフィギュレーションROM搭載 ■ クロック 50MHz ECS-300がディスコンとなりました ■ FPGAへのコンフィギュレーションとROMへのISPが可能な7ピンJTAGコネクタ装備 ■ JTAG Buffer回路で、安定したダウンロードを実現 ■ 3.3V単一電源 1.2Vをボード内で生成 ■ コンフィギュレーション用リセット回路 ■ セミカードサイズ: 54mmX53mm ■ 4層基板 ■

|

||||||||||||||||||||

| XCMシリーズについて XCM-3シリーズはすべてセミカードサイズでI/Oピンの配置が同一となっています。1ピン位置、共通外形図、DXFデータなどは  をご覧下さい。 をご覧下さい。※当社ではサンプル回路やリファレンス回路はご用意しておりません。 |

|||||||||||||||||||||

| 品名 | MODEL | 実装FPGA | 製品状況 | 直販価格 | 購入 | サポート |

| Spartan-3A VQG100 ブレッドボード | XCM-304-200A | XC3S200A-4VQG100C |  |

- | お問合せ |