| XCM-111 シリーズ Spartan-6 LXT FGG484 搭載ブレッドボード 発売中 |

|

||

2011/08/23-

Spartan-6 LXTの評価や試作にご活用いただけます。

XCM-111シリーズは在庫限りで、販売を終了いたします。受注生産をご希望の方はお問合せください。

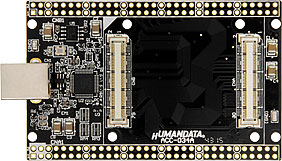

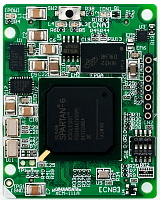

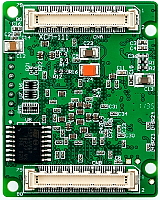

XCM-111シリーズは在庫限りで、販売を終了いたします。受注生産をご希望の方はお問合せください。 クリックして拡大  クリックして拡大 |

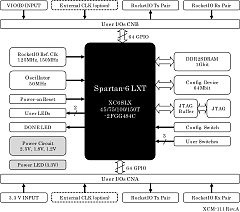

■ XC6SLX45T-2FGG484C, XC6SLX75T-2FGG484C XC6SLX100T-2FGG484C または XC6SLX150T-2FGG484Cを搭載 ■ 豊富なI/Oを外部引き出し(128本) ■ オンボードクロック 50MHz(LVTTL) 125MHz、150MHz(LVDS、RocketIO用リファレンスクロック) 125/150MHzと通信規格について ■ コンフィギュレーションSPI-ROM Micron: M25P64 (64Mbit) iMPACTからISP可能 ■ DDR2SDRAM MT47H64M16HR-3:H, (1Gbit) 2Gbit搭載可能(カスタムオーダー) ■ 汎用スイッチ 押しボタン x1 スライド x2 ■ 汎用LED x2 ■ RocketIO評価可能 Txペア/Rxペア 各2チャンネル ■ FPGAへのコンフィグレーションとROMへのISPが可能な7ピンJTAGコネクタ装備 Buffer回路で、安定したダウンロードを実現 ■ 3.3V単一電源動作 1.2V、1.8V、2.5Vをボード内で生成 ■ CNBのVccoを分離可能(製造時には3.3Vでテスト) ■ コンフィギュレーション用リセット機能 ■ 10層基板 ■ ハーフカードサイズ 54mm x 43mm

[ZKB-031KIT] |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

ブロック図 クリックして拡大 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

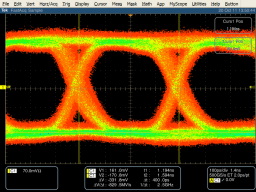

高速トランシーバのアイパターン例 Device: LX75T Board: ZKB-103 Channel: GTP 101(0) Tx(P) Ref.Clk: 125MHz Rate: 2.5Gbps Swing: 785mV Pre-emphasis: 0% Data: PRBS-7 Trigger: Rising Edge |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| XCMシリーズについて XCM-1シリーズはすべてハーフカードサイズでI/Oピンの配置が同一となっています。1ピン位置、共通外形図、DXFデータなどは  をご覧下さい。 をご覧下さい。※XCM-1LシリーズとはI/O電圧の仕様が異なるため置き換えできません。 ※当社ではサンプル回路やリファレンス回路はご用意しておりません。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

XCM-111シリーズは在庫限りで、販売を終了いたします。受注生産をご希望の方はお問合せください。

XCM-111シリーズは在庫限りで、販売を終了いたします。受注生産をご希望の方はお問合せください。