営業日カレンダー

土日と、平日のピンク枠日は休業日です。在庫品につきましては、ご注文当日発送または翌営業日発送となっております。

※当日発送は原則弊社営業日15時までのご注文とさせて頂きます。

土日と、平日のピンク枠日は休業日です。在庫品につきましては、ご注文当日発送または翌営業日発送となっております。

※当日発送は原則弊社営業日15時までのご注文とさせて頂きます。

ACM-107シリーズは、Altera社の高性能FPGAである Cyclone IV EのFBGA484pinを搭載した、FPGAボードです。ハーフカードサイズに、豊富な機能を搭載しています。

Cyclone IV Eの評価や試作にご活用いただけます。

ACM-107シリーズは Rev2に切り替わりました。

コンフィギュレーションROM EPCS16SI8N、EPCS64SI16Nのディスコン(製造中止)により、代替品の EPCQ16ASI8N、EPCQ64ASI16N に変更しました。現行のリビジョンがなくなり次第、Rev2に切り替わります。(併売中)

Alteraシリーズ コンフィギュレーションROM ディスコンによる対応について

| FPGAの概要 | EP4CE55 | EP4CE75 | EP4CE115 |

|---|---|---|---|

| Logic Elements | 55,856 | 75,408 | 114,480 |

| Embedded memory (kb) | 2,340 | 2,745 | 3,888 |

| M9K RAM blocks | 260 | 305 | 432 |

| Embedded 18 x 18 Multipliers | 154 | 200 | 266 |

| General-purpose PLLs | 4 | 4 | 4 |

| Global Clock Networks | 20 | 20 | 20 |

| Maximum user I/O pins (Device) | 374 | 426 | 528 |

| Maximum user I/O pins (Board) | 128 | 128 | 128 |

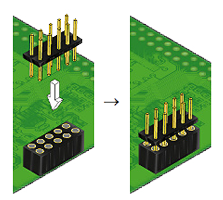

JTAGコネクタはソケットになっています。使用するときにはピンヘッダを実装してください。(当社採用のソケットは、0.64mm角ピンに対応したものです)

詳細は「JTAG(ISP)ピンレイアウトについて」のページをご確認ください。

| CNA | CNB | LVDS用 ターミネータ 実装可能数 |

A基板 |

|---|---|---|---|

| IOA0-63: MAX 20 mm MIN 16 mm |

IOB0-63: MAX 33 mm MIN 29 mm |

(図面参照) |

デバイスのI/Oピンがそのまま外部(パッドまたはコネクタ等)に引き出されています。デバイスと同じように扱って下さるようお願いいたします。

「使用上のご注意」にご注意いただきたい内容を掲載しております。

ACM-1シリーズはすべてハーフカードサイズでI/Oピンの配置が同一となっています。1ピン位置、共通外形図、DXFデータなどは共通資料ページをご覧下さい。

| 品名 | 型番 | 実装FPGA | 在庫状況 | 直販価格 | 購入方法 | |

|---|---|---|---|---|---|---|

| ACM-107-55C8 | 掛売/商社様経由など | |||||

| ACM-107-75C8 | ||||||

| ACM-107-75C7 | ||||||

| ACM-107-115C8 | ||||||

製品の仕様、価格など、改良のため予告無く変更になることがございます。製品資料ページに公開されている以外の資料はご用意しておりません。また納入仕様書の発行はいたしておりません。