2002/04/12-

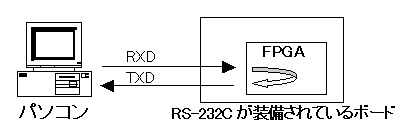

パソコンに標準で装備されているRS-232Cを使って、RS-232Cが装備されているボードと通信をするためのVHDLファイルを公開します。下図のように1バイト送信し、FPGAでエコーする回路を例に説明します。ハイパーターミナル等の通信ソフトで動作を確認することができます。この回路を利用することに制限はありませんが、ご使用にはお客さまの責任でお願いします。使用した結果について弊社は一切関知いたしません。

▼概略図

▼通信オプション

| ボーレート | 115.2k bps |

| データ | 8ビット |

| パリティ | なし |

| ストップビット | 1ビット |

| フロー制御 | なし |

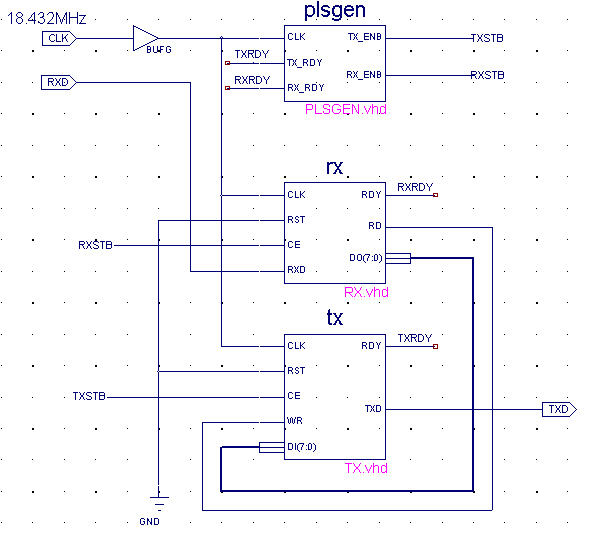

エコー回路を作成する場合は以下のように配線してください。

▼最上位回路図

▼VHDLソース

RX.vhd

TX.vhd

PLSGEN.vhd

| ボーレート | TX_WIDTH | RX_WIDTH | N |

| 115200 | 8 | 4 | 160 |

| 57600 | 9 | 5 | 320 |

| 38400 | 9 | 5 | 480 |

| 19200 | 10 | 6 | 960 |

| 14400 | 11 | 7 | 1280 |

| 9600 | 11 | 7 | 1920 |

| 4800 | 12 | 8 | 3840 |

| 2400 | 13 | 9 | 7680 |

| 1200 | 14 | 10 | 15360 |

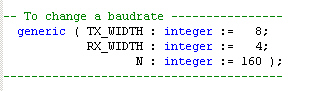

ボーレートを変更する場合は上表のパラメータをPLSGEN.vhdファイルの以下の部分を変更して下さい。システムクロックは18.432MHzの場合です。