MIG(MCB)によるDDR2 SDRAMアクセス方法について

XCMシリーズ搭載DDR2 SDRAM操作のヒント

2011/02/07 -

ユーザさまご自身で内部回路はすべて設計していただくことになります。

当社でも製品検査のために何らかの方法でDDR2 SDRAへの操作が必要になりますの皆さまのヒントになればと考えて概略のご説明を致します。

当社では、Xilinx社の提供する開発ツールISEに含まれるMIGという手段を利用してメモリアクセスを行って製品検査に利用しております。

本ページでは、MIGを使用して、DDR2SDRAMへのアクセスが確認できるまでの手順の概略を以下にお示しします。

ISEやMIGなどの詳細はXILINX社サイトや開発ツールのHELP、開発ツールの同梱資料などをご参照くださいませ。

◆ISEプロジェクト

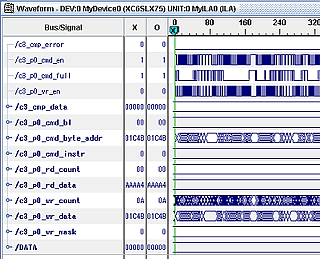

◆ChipScopeで観測

◆ご参考

◆お問い合わせ

・編集時のISEのバージョンは12.2 M63c、MIGのバージョンは3.5です(今後のバージョンアップにより手順が大幅に異なる可能性があります)

Spartan6ではMCB(Memory controller block)というメモリ専用ハードウェアが搭載されています。

Core generatorを起動し、希望するデバイスでプロジェクトを作成します。

Memories & Storage Elements → Memory Interface GeneratorsからMIGを起動します。

(とくに変更のない箇所は省略しております)

(クリックして全体表示)

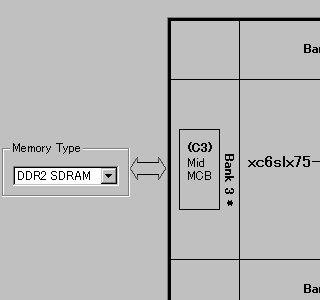

(クリックして全体表示)BANK3にDDR2SDRAMを選択します。

(クリックして全体表示)

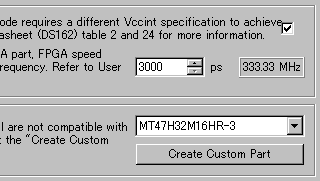

(クリックして全体表示)メモリパーツと動作周波数を設定します。

データの転送レートは設定した周波数の二倍になります。

(クリックして全体表示)

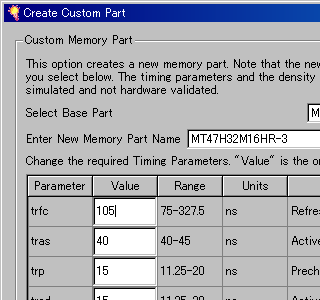

(クリックして全体表示)Memory Partには、XCM-018に搭載されている「MT46H32M16HR-3」が一覧にありませんので「Create Custom Part」から作成します。

「MT47H64M16XX-25」をベースにして

・trfcを105ns

・Bank Addressを2

に変更し、名前を入力してSaveをクリックします。

Output Drive StrengthはReduced strengthに設定しました。

ポートの設定は「One 128-bit bi-directional port」としました。

Pinターミネーションには「Clibrated input termination」を選択し、

・RZQ=Y2

・ZIO=W3

としています。(デフォルト設定)

(クリックして全体表示)

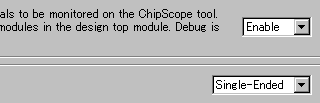

(クリックして全体表示)ChipScopeを使用しますので「Debug Signal for Memory Controller」を有効にしています。

オンボードクロックがシングルエンドですので、「System Clock」を「Single-Ended」としています。

最後にメモリのシミュレーションモデル生成のためにライセンスに同意し、Generateをクリックします。

MIGの設定は以上です。

MIGにより生成されたフォルダにはexample_designとuser_designの二つのフォルダが生成されています。

前者のexample_designにはTraffic Pattern Generatorが含まれている、動作確認用のものとなっています。

(生成したフォルダ)\(MIGのコンポーネント名)\example_design\par\create_ise.bat

を実行するとISEプロジェクトが生成されます。

ChipScope用のファイル(icon, ila, vio)がインポートされていませんでしたので、同階層にある各*.xcoファイルを追加しました。

MIGのデザインでは、TOPから入力するクロックをそのまま無逓倍でMCBに供給するようになっています。

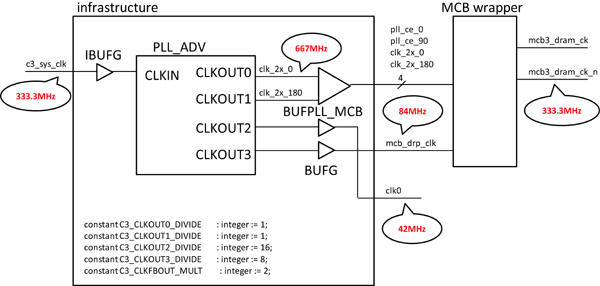

今回のMIGの設定では、デフォルトでのクロック設定は上図のようになっていました。

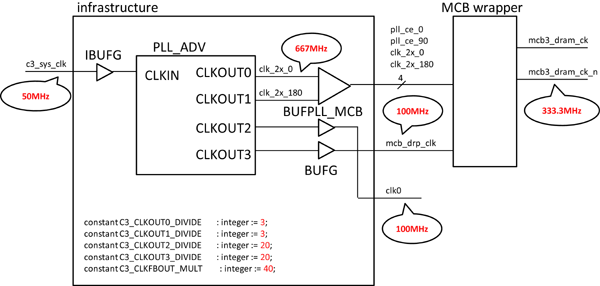

しかし、オンボードクロックは50MHzですので、上図のようにメモリ用PLLに逓倍させます。

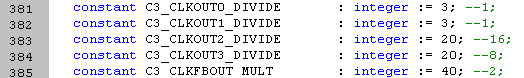

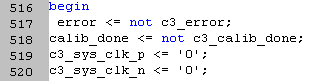

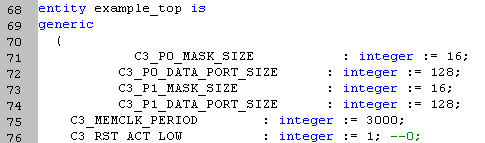

上図を設定するため、top階層のコードをいくつか編集します。

inftastructureに渡されるconstantを書き換え。

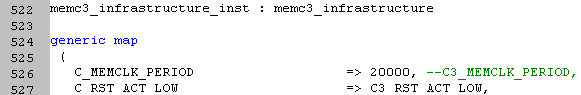

infrastructureに渡される周期の値を50MHzに変更します。

LED出力とリセット入力の極性も合わせておきます。

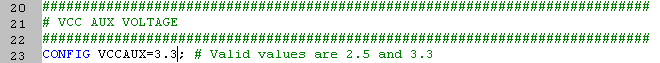

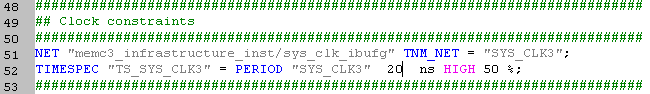

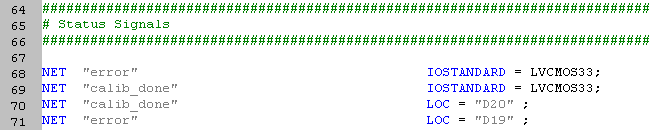

引き続きUCFの設定をXCM-018の仕様に合わせます。

VCCAUXには3.3Vが接続されていますので、2.5から変更します。

IBUFGの出力は50MHzのタイミング制約に修正します。

ステータス通知用の出力はオンボードLEDにアサインします。

クロック入力をリセット入力を適当なピンにアサインします。

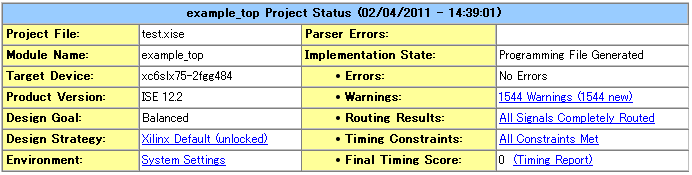

以上で修正が完了しましたのでImplementを実行します。

エラー無くインプリメントが完了しました。

(クリックして全体表示)

(クリックして全体表示)cmp_errorが立つことなく、正常にアクセスできていることが確認できます。

プロジェクトの作成には、下記資料を参考にしております。

Xilinx UG388 Spartan-6 FPGA Memory Controller User Guide

Xilinx UG416 Spartan-6 FPGA Memory Interface Solutions User Guide

当社では、サンプル回路などのご提供は行っておりません。あしからずご了承くださいませ。

間違いなど見つけられましたらぜひご指摘下さい。