2008/04/02-

当社のFPGAボードはFPGAのI/Oピンがそのままパッドやコネクタにでています。

取扱はFPGAそのものを取り扱うのと同様にお願いいたします。

- FPGAボードを手に取るときは、FPGAボードを置いた作業机などにまず触れ、自分の電位とFPGAボードの電位を合わせる

- ボードを誰かに手渡すときは、まず握手するなどして相手の人と電位を合わせる

- ボードの梱包には制電対策品をつかう

- 静電気対策をした作業環境を用意する(制電マット、制電カーペット、制電椅子、制電手袋など)

FPGAの静電気耐量はどれくらい?

FPGAが高性能になればなるほど微細加工で製造されています。一般的なRS-232Cトランシーバなどがヒューマンモデルで±15,000V以上あるのにたいして、FPGAでは±2,000V以下となっています。

静電気でパチッと感じた経験がおありだと思います。そのとき3,000Vから10,000V以上にもなるそうです。

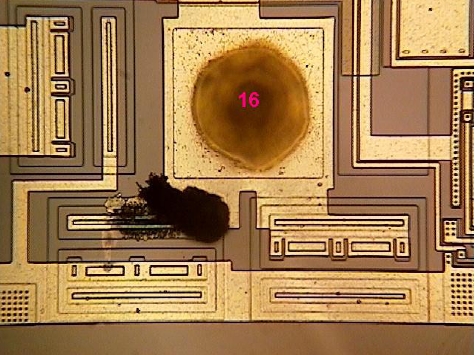

ESD破壊された部分の顕微鏡写真(当社製品での実例)。FPGAでは有りません。

ESD破壊された部分の顕微鏡写真(当社製品での実例)。FPGAでは有りません。- FPGAボードにオシロやロジアナ、ダウンロードケーブルを接続するときは、全体のFGをとってGND電位をそろえる

- 通電したままダウンロードケーブルや、I/Oコネクタを挿抜しない

パラレルポートを接続した瞬間に、ノートパソコンのパラレルが故障した例や、USB機器を接続した瞬間にUSBポートが焼損した例も報告されています。

■ボードなどを手渡すときは、自分の手で帯電防止マットを敷いたデスクをさわり、ボードをその上に置く。受け取る人はまず手を帯電防止台にさわり、その後ボードを受け取る。台が無いときはまず握手してから、その後に手渡す。なるべく基板むき出しで手渡さない。

■作業を始めるときは、作業台の帯電防止マットにまず触る。

セルフのガソリンスタンドの放電パッドを思い出して下さい。