2002/07/18-

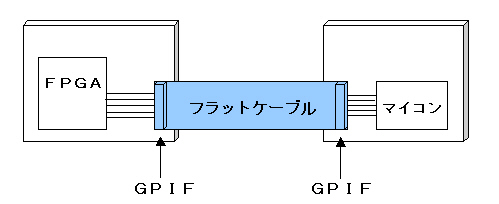

ボード間のコネクタの信号配置パターンが異なる場合,半田付けなどの作業が必要となり,ボード間の接続に手間がかかります.コネクタのピン配置が同じであれば,ワンタッチで接続することができます.FPGAはピン定義ファイルによって,入力や出力,ピン番号が定義されます.電源ピンやクロックピンの配置が同じであれば,汎用性のあるパターンを作ることができます.これによって,より短時間で接続が可能で,データの送受信を円滑に行えます.また,誤って信号をショートさせる危険性も少なくなります.このような外部拡張コネクタを有するボードを,GPIF搭載のボードと呼ぶことにします.例えば,図1のようにピン配置の異なるマイコンであっても,FPGAであればピンの配置を変えることで接続は可能です.

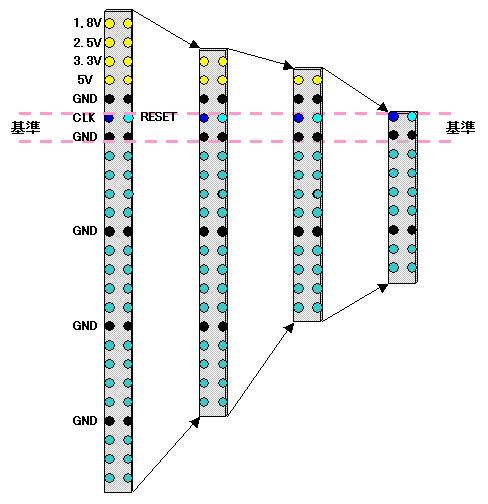

GPIFは最大50ピンコネクタで,フラットケーブルで接続します.ピン配置を規則的な繰り返しパターンにすることにより,コネクタのサイズを大きくしたり小さくしたりできるスケーラブルな構造になっています(図2).CLK,RESET,GNDを基準として必要に応じてピン数を変更できます.GNDを強化するために,任意の入出力線8ビットごとに,GND線を2本配置しています.また,5Vから1.8Vまで4種類の電源ラインを持つことができ,少量の電流であれば,接続するボードに電源を供給することが可能です.CLKはFPGAなどで,分周したクロックをターゲットのボードに供給することを目的としており,RESETは電源供給時におけるパワーオンリセットなどに使用します.最大50ピンコネクタの場合は表1のような配置となります.

▼概略図 (図1)

▼スケーラブルなピン配置 (図2)

▼最大50ピンコネクタの場合 (表1)

| 1 | 1.8V | 2 | 1.8V |

| 3 | 2.5V | 4 | 2.5V |

| 5 | 3.3V | 6 | 3.3V |

| 7 | 5V | 8 | 5V |

| 9 | GND | 10 | GND |

| 11 | CLK | 12 | RESET |

| 13 | GND | 14 | GND |

| 15 | I/O 0 | 16 | I/O 1 |

| 17 | I/O 2 | 18 | I/O 3 |

| 19 | I/O 4 | 20 | I/O 5 |

| 21 | I/O 6 | 22 | I/O 7 |

| 23 | GND | 24 | GND |

| 25 | I/O 8 | 26 | I/O 9 |

| 27 | I/O 10 | 28 | I/O 11 |

| 29 | I/O 12 | 30 | I/O 13 |

| 31 | I/O 14 | 32 | I/O 15 |

| 33 | GND | 34 | GND |

| 35 | I/O 16 | 36 | I/O 17 |

| 37 | I/O 18 | 38 | I/O 19 |

| 39 | I/O 20 | 40 | I/O 21 |

| 41 | I/O 22 | 42 | I/O 23 |

| 43 | GND | 44 | GND |

| 45 | I/O 24 | 46 | I/O 25 |

| 47 | I/O 26 | 48 | I/O 27 |

| 49 | I/O 28 | 50 | I/O 29 |