# HUMANDATA

Spartan-3 ブレッドボード (カードサイズ) XCM-008 ユーザーズマニュアル Ver. 2.2

ヒューマンデータ

# 目 次

|    | · はじめに                      | 1  |

|----|-----------------------------|----|

| •  | ご注意                         | 1  |

| •  | 改訂記録                        | 2  |

| 1. | 製品の内容について                   | 3  |

| 2. | 仕様                          | 3  |

| 3. | 製品概要                        | 4  |

|    | 3.1 各部の名称                   | 4  |

|    | 3.2 ブロック図                   | 4  |

|    | 3.3 電源入力                    | 5  |

|    | 3.4 JTAG コネクタ               | 5  |

| 4. | FPGA のコンフィギュレーション           | 6  |

| 5. | コンフィギュレーション ROM へのデータ書き込み方法 | 7  |

| 6. | コンフィギュレーション ROM データの作成方法    | 8  |

| 7. | ジャンパスイッチの説明                 | 10 |

| 8. | FPGA ピン割付け表                 | 11 |

|    | 8.1 CNA                     | 11 |

|    | 8.2 CNB                     |    |

|    | 8.3 オンボードクロック               | 12 |

| 9. | 参考資料について                    | 13 |

| 10 | ). 付属資料                     | 13 |

|    |                             |    |

#### ● はじめに

この度は、Spartan-3 ブレッドボード/XCM-008 シリーズをお買い上げいただきまして誠にありがとうございます。

XCM-008 シリーズは、XILINX の高性能 FPGA Spartan-3(XC3S)を用いた評価用ボードで、電源回路、リセット回路、クロック回路、コンフィギュレーション回路、コンフィギュレーション ROM、などを装備した、使いやすいボードになっています。どうぞご活用ください。

### ● ご注意

禁止

- 1. 本製品には、民生用の一般電子部品が使用されています。 宇宙、航空、医療、原子力等、各種安全装置など人命、事故にかかわる特別 な品質、信頼性が要求される用途でのご使用はご遠慮ください。

- 2. 水中、高湿度の場所での使用はご遠慮ください。

- 3. 腐食性ガス、可燃性ガス等引火性のガスのあるところでの使用はご遠慮ください。

- 4. 基板表面に他の金属が接触した状態で電源を入れないでください。

- 5. 定格を越える電源を加えないでください。

注意

- 8. 本製品の運用の結果につきましては、7. 項にかかわらず当社は責任を負いかねますので、ご了承願います。

- 9. 本書に記載されている使用と異なる使用をされ、あるいは本書に記載されていない使用をされた場合の結果については、当社は責任を負いません。

- 10. 本書および、回路図、サンプル回路などを無断で複写、引用、配布することは お断りいたします。

- 11. 発煙や発火、異常な発熱があった場合はすぐに電源を切ってください。

- 12. ノイズの多い環境での動作は保障しかねますのでご了承ください。

- 13. 静電気にご注意ください。

## ● 改訂記録

| 日付         | バージョン | 改訂内容                                  |

|------------|-------|---------------------------------------|

| 2010/05/24 | 2.2   | ECS-300(72KHz,18.432MHz)のディスコンによる仕様変更 |

XCM-008 Ver. 2.2

2

### 1. 製品の内容について

本パッケージには、以下のものが含まれています。万一、不足などがございましたら、弊 社宛にご連絡ください。

FPGA ブレッドボード XCM-008 シリーズ1付属品1マニュアル(本書)1\*ユーザー登録はがき1\*\* オーダー毎に各 1 部の場合があります。(ご要望により追加請求できます。)

### 2. 仕様

| 製品型番         | XCM-008-50                              | XCM-008-200      | XCM-008-400      |  |  |  |

|--------------|-----------------------------------------|------------------|------------------|--|--|--|

| 搭載 FPGA      | XC3S50-4TQG144C                         | XC3S200-4TQG144C | XC3S400-4TQG144C |  |  |  |

| コンフィグ ROM    | XCF01SVOG20C                            | XCF01SVOG20C     | XCF02SVOG20C     |  |  |  |

| 電源           | DC 3.3V (内部電源はオン                        | ボードレギュレータにより生    | 成)               |  |  |  |

| 消費電流         | N/A (詳細は FPGA データ                       | シートご参照)          |                  |  |  |  |

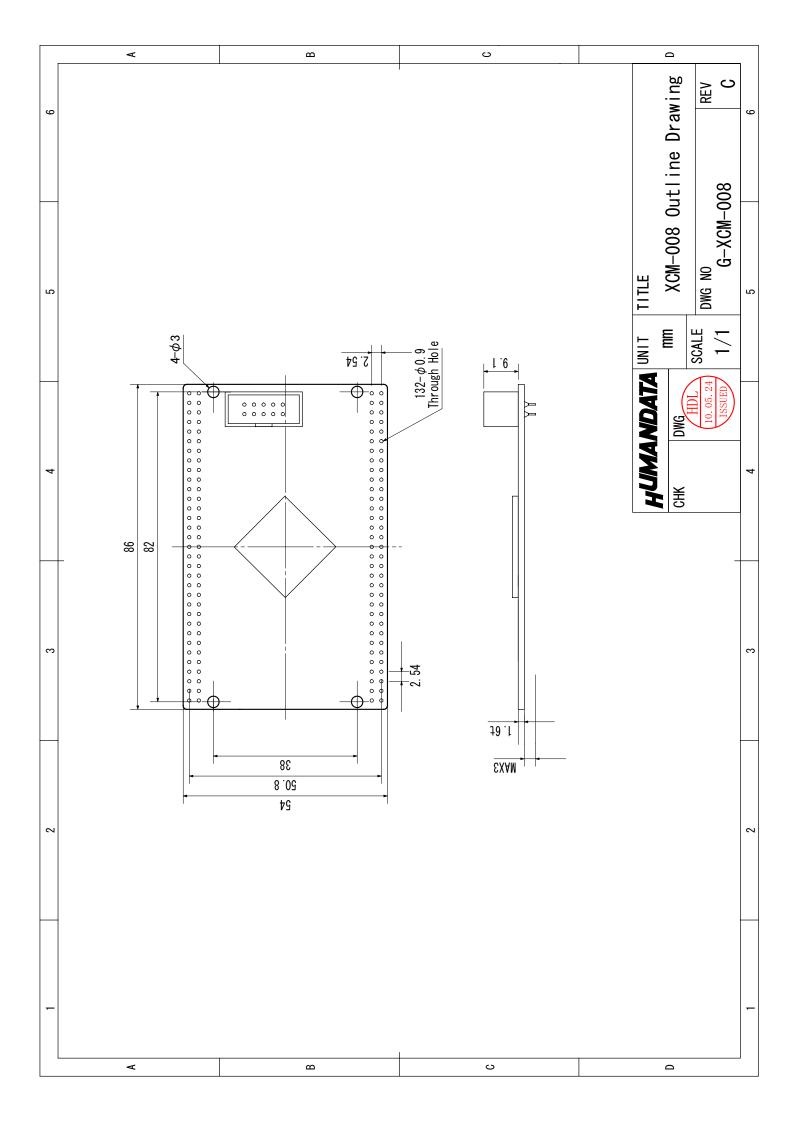

| 外形寸法         | 86 × 54 [mm]                            |                  |                  |  |  |  |

| 質量           | 約 25 [g]                                |                  |                  |  |  |  |

| ユーザ I/O      | 91 本                                    |                  |                  |  |  |  |

| I/O コネクタ     | 66 ピンスルーホール 0.9[mm φ ] × 2 組 2.54mm ピッチ |                  |                  |  |  |  |

| プリント基板       | ガラスエポキシ 4 層基板 1.6t                      |                  |                  |  |  |  |

| クロック         | オンボード 48MHz (外部供給可能)                    |                  |                  |  |  |  |

| コンフィグ用リセット回路 | 内蔵(200ms TYP)                           | 内蔵(200ms TYP)    |                  |  |  |  |

| JTAG コネクタ    | DIL10 ピンソケット 2.54mm ピッチ                 |                  |                  |  |  |  |

| ステータス LED    | 2個(POWER、DONE)                          |                  |                  |  |  |  |

| → 屋 □        | DIL80 ピンヘッダ(任意にた                        | リット可能) 2 本       |                  |  |  |  |

| 付属品          | ジャンパソケット 2個                             |                  |                  |  |  |  |

### 3. 製品概要

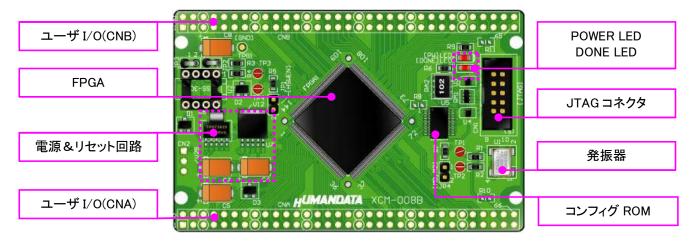

#### 3.1 各部の名称

部品面

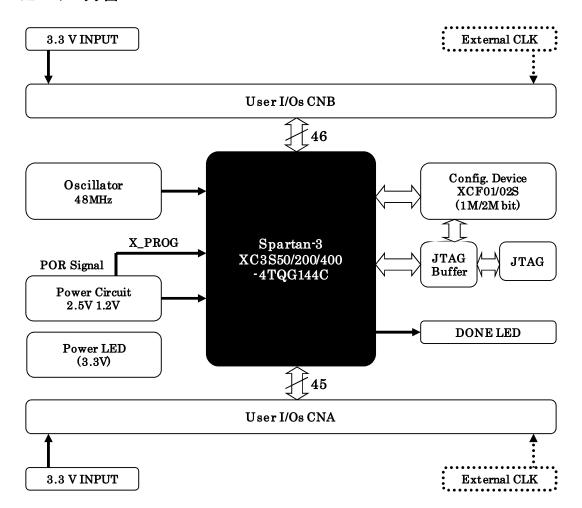

#### 3.2 ブロック図

#### 3.3 電源入力

本ボードは、DC 3.3V単一電源で動作します。内部で必要な、2.5V、1.2V はオンボードの レギュレータにより生成されます。外部から供給する3.3V電源は充分安定して、充分な余裕 のあるものをご用意ください。

電源は、CNA、CNB から供給してください。また電源の立ち上がりは単調増加である必要があります。良質の電源を使用するようにしてください。

VCCO は2系統に分かれておりますので、全て正しく接続してください。

#### 3.4 JTAG コネクタ

FPGA へのコンフィギュレーション、内蔵の ISP 可能なシリアル ROM への書き込みに用います。ピン配置は次表のとおりです。

| 信号名 | ピン | 番号 | 方向        |

|-----|----|----|-----------|

| TCK | 1  | 2  | GND       |

| TDO | 3  | 4  | VCC(3.3V) |

| TMS | 5  | 6  | -         |

| _   | 7  | 8  | -         |

| TDI | 9  | 10 | GND       |

弊社製ダウンロードケーブル XC3 の 10 ピンコネクタと 1:1 で対応しています。 XILINX 社の純正ケーブルを用いることもできます。

#### 注意

ダウンロードケーブルとコネクタの対応に注意して接続して下さい。

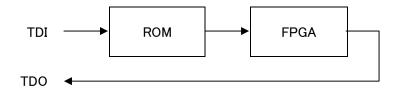

JTAG チェインには ROM と FPGA の両方が接続されています。

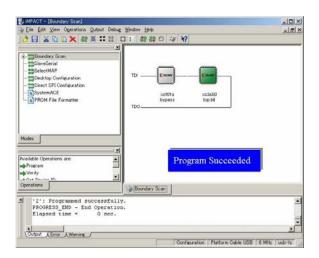

#### 4. FPGA のコンフィギュレーション

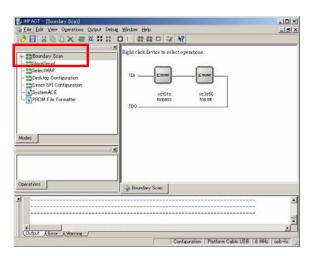

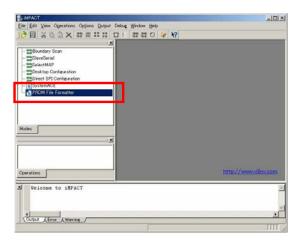

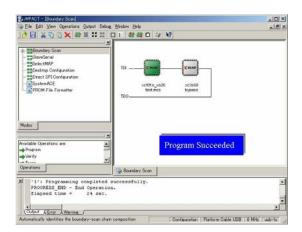

1. FPGA へのコンフィギュレーションは iMPACT により行います。 iMPACT を起動し、右図赤枠 [Boundary Scan]をダブルクリックします。[File]-[Initialize Chain]をクリックすると、ROMとFPGAが認識されます。ROMは任意の mcs ファイル、または BYPASS とし、FPGA に対して bit ファイルを割り付けてください。

デバイスのアイコン上で右クリック をし、Program…をクリックします。

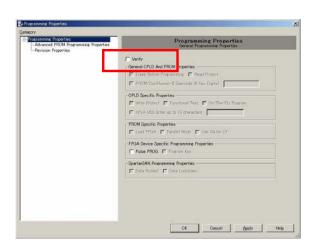

FPGA へのコンフィギュレーション の際は、通常 Verify のチェックを外 してください。

3. 書き込みが成功すると、Program Succeeded と表記されます。

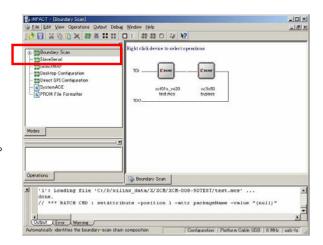

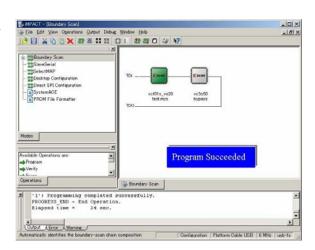

### 5. コンフィギュレーション ROM へのデータ書き込み方法

1. ROM へのデータ書込みは iMPACT により行います。

右図赤枠[Boundary Scan]をダブル クリックします。iMPACT を起動し [File]-[Initialize Chain]をクリックす ると、ROMとFPGAが認識されます。 JTAG は任意の bit ファイル、また は BYPASS とし、ROM に対して mcs ファイルを割り付けてください。

デバイスのアイコン上で右クリックをし、[Program…]をクリックします。

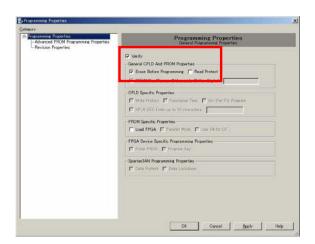

ROM へのデータ書き込み時は

[Verify] [Erase Before Programming]

にチェックをいれ OK をクリックします。

Program Succeeded が表示されれば 終了です。

### 6. コンフィギュレーション ROM データの作成方法

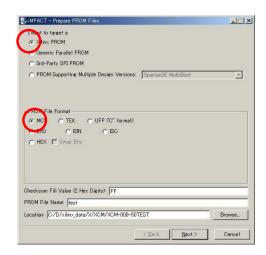

1. 右図 赤枠[PROM File Formatter]上でダブルクリックします。

次に、右図のようにチェックを入れ、

File Name と Location(保存先)を指定 し Next>をクリックします。

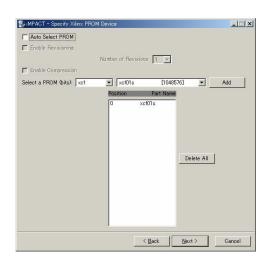

次に、PROMの種類を指定しAddをクリックします。

(XCM-008-50、XCM-008-200 の場合は xcf01s を指定、XCM-008-400 の場合は xcf02s 指定します) 右図のようになれば Next>をクリック

します。

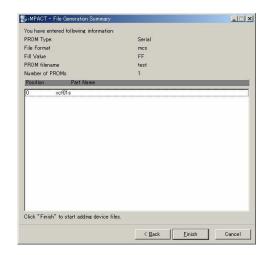

4. 次に、Finish をクリックします。

5. 次に、下図ダイアログが表示されますので **OK** をクリックし、bit ファイルを指定します。

6. 次に、No をクリックします。

7. 次に、OK をクリックします。

8. 次に、PROM Formatter タブの、表示 エリアで右ボタンメニューの Generate File をクリックします。

PROM File Generation Succeeded が表示されれば ROM データの完成です。

### 7. ジャンパスイッチの説明

JP4: M0,M2 信号 設定用

M1 は 0 に固定(回路図参照)

JP4 により、M0 と M2 は同時に 1 または 0 に設定されます。

Table 21: Spartan-3 Configuration Mode Pin Settings

| Configuration Mode <sup>(1)</sup> | Mo | M1 | M2 | Synchronizing Clock | Data Width | Serial DOUT(2) |

|-----------------------------------|----|----|----|---------------------|------------|----------------|

| Master Serial                     | 0  | 0  | 0  | CCLK Output         | 1          | Yes            |

| Slave Serial                      | 1  | 1  | 1  | CCLK Input          | 1          | Yes            |

| Master Parallel                   | 1  | 1  | 0  | CCLK Output         | 8          | No             |

| Slave Parallel                    | 0  | 1  | 1  | CCLK Input          | 8          | No             |

| JTAG                              | 1  | 0  | 1  | TCK Input           | 1          | No             |

- The voltage levels on the M0, M1, and M2 pins select the configuration mode.

The daisy chain is possible only in the Serial modes when DOUT is used.

(Xilinx 社データシートより)

#### ROM 使用時: Master Serial mode

JP4 ショート M0 = 0

M1 = 0 (固定)

M2 = 0

#### 出荷時:JTAG mode

JP4 オープン M0 = 1

M1 = 0 (固定)

M2 = 1

#### JP1: HSWAP ENABLE ピンの設定

FPGA の HSWAP\_ENABLE ピンの設定を行います。

JP1 ショート :0

JP1 オープン:1

(出荷時はオープン)

### 8. FPGA ピン割付け表

#### 8.1 CNA

| BANK | NET LABEL | FPGA         | CNA |    | FPGA | NET LABEL | BANK |

|------|-----------|--------------|-----|----|------|-----------|------|

|      | V33_A     | 3.3V         | 1   | 2  | 3.3V | V33_A     |      |

|      | 電源予約      | 電源予約         | 3   | 4  | 電源予約 | 電源予約      |      |

|      | GND       | GND          | 5   | 6  | GND  | GND       |      |

| Α    | IOA0      | 1            | 7   | 8  | 2    | IOA1      | Α    |

| Α    | IOA2      | 4            | 9   | 10 | 5    | IOA3      | Α    |

| Α    | IOA4      | 6            | 11  | 12 | 7    | IOA5      | Α    |

| Α    | IOA6      | 8            | 13  | 14 | 10   | IOA7      | Α    |

|      | GND       | GND          | 15  | 16 | GND  | GND       |      |

| Α    | IOA8      | 11           | 17  | 18 | 12   | IOA9      | Α    |

| Α    | IOA10     | 13           | 19  | 20 | 14   | IOA11     | Α    |

| Α    | IOA12     | 15           | 21  | 22 | 17   | IOA13     | Α    |

| Α    | IOA14     | 18           | 23  | 24 | 20   | IOA15     | Α    |

|      | GND       | GND          | 25  | 26 | GND  | GND       |      |

| Α    | IOA16     | 21           | 27  | 28 | 23   | IOA17     | Α    |

| Α    | IOA18     | 24           | 29  | 30 | 25   | IOA19     | Α    |

| Α    | IOA20     | 26           | 31  | 32 | 27   | IOA21     | Α    |

| Α    | IOA22     | 28           | 33  | 34 | 30   | IOA23     | Α    |

|      | GND       | GND          | 35  | 36 | GND  | GND       |      |

| Α    | IOA24     | 31           | 37  | 38 | 32   | IOA25     | Α    |

| Α    | IOA26     | 33           | 39  | 40 | 35   | IOA27     | Α    |

| Α    | IOA28     | 36           | 41  | 42 | 40   | IOA29     | Α    |

| Α    | IOA30     | 41           | 43  | 44 | 44   | IOA31     | Α    |

|      | GND       | GND          | 45  | 46 | GND  | GND       |      |

| Α    | IOA32     | 46           | 47  | 48 | 47   | IOA33     | Α    |

| Α    | IOA34     | 50           | 49  | 50 | 51   | IOA35     | Α    |

| Α    | IOA36     | 52           | 51  | 52 | 53   | IOA37     | Α    |

| Α    | IOA38     | 70           | 53  | 54 | 59   | IOA39     | Α    |

|      | GND       | GND          | 55  | 56 | GND  | GND       |      |

| Α    | IOA40     | 60           | 57  | 58 | 63   | IOA41     | Α    |

| Α    | IOA42     | 68           | 59  | 60 | 69   | IOA43     | Α    |

| Α    | IOA44     | 57 <b>*1</b> | 61  | 62 | N.C  | N.C       | Α    |

| Α    | N.C       | N.C          | 63  | 64 | N.C  | N.C       | Α    |

| Α    | N.C       | N.C          | 65  | 66 | 56   | CLK1 *2   | Α    |

- \*1 FPGA ピン#57 は DOUT/BUSY ピンです。コンフィギュレーション中は出力ピンとなります。 コンフィギュレーション後に I/O として使用できますが、出力として使用することを推奨します。 詳細は FPGA のデータシートをご覧下さい。

- \*2 抵抗 R10 実装により FPGA ピン# 56 (CLK1) に接続可能

#### 8.2 CNB

| BANK | NET LABEL | FPGA | CNB |    | FPGA | NET LABEL      | BANK |

|------|-----------|------|-----|----|------|----------------|------|

|      | V33_B     | 3.3V | 1   | 2  | 3.3V | V33_B          |      |

|      | 電源予約      | 電源予約 | 3   | 4  | 電源予約 | 電源予約           |      |

|      | GND       | GND  | 5   | 6  | GND  | GND            |      |

| В    | IOB0      | 141  | 7   | 8  | 140  | IOB1           | В    |

| В    | IOB2      | 137  | 9   | 10 | 135  | IOB3           | В    |

| В    | IOB4      | 132  | 11  | 12 | 131  | IOB5           | В    |

| В    | IOB6      | 130  | 13  | 14 | 129  | IOB7           | В    |

|      | GND       | GND  | 15  | 16 | GND  | GND            |      |

| В    | IOB8      | 125  | 17  | 18 | 124  | IOB9           | В    |

| В    | IOB10     | 123  | 19  | 20 | 122  | IOB11          | В    |

| В    | IOB12     | 119  | 21  | 22 | 118  | IOB13          | В    |

| В    | IOB14     | 116  | 23  | 24 | 113  | IOB15          | В    |

|      | GND       | GND  | 25  | 26 | GND  | GND            |      |

| В    | IOB16     | 112  | 27  | 28 | 108  | IOB17          | В    |

| В    | IOB18     | 107  | 29  | 30 | 105  | IOB19          | В    |

| В    | IOB20     | 104  | 31  | 32 | 103  | IOB21          | В    |

| В    | IOB22     | 102  | 33  | 34 | 100  | IOB23          | В    |

|      | GND       | GND  | 35  | 36 | GND  | GND            |      |

| В    | IOB24     | 99   | 37  | 38 | 98   | IOB25          | В    |

| В    | IOB26     | 97   | 39  | 40 | 96   | IOB27          | В    |

| В    | IOB28     | 95   | 41  | 42 | 93   | IOB29          | В    |

| В    | IOB30     | 92   | 43  | 44 | 90   | IOB31          | В    |

|      | GND       | GND  | 45  | 46 | GND  | GND            |      |

| В    | IOB32     | 89   | 47  | 48 | 87   | IOB33          | В    |

| В    | IOB34     | 86   | 49  | 50 | 85   | IOB35          | В    |

| В    | IOB36     | 84   | 51  | 52 | 83   | IOB37          | В    |

| В    | IOB38     | 82   | 53  | 54 | 80   | IOB39          | В    |

|      | GND       | GND  | 55  | 56 | GND  | GND            |      |

| В    | IOB40     | 79   | 57  | 58 | 78   | IOB41          | В    |

| В    | IOB42     | 77   | 59  | 60 | 76   | IOB43          | В    |

| В    | IOB44     | 74   | 61  | 62 | 73   | RESET *3       | В    |

| В    | N.C       | N.C  | 63  | 64 | N.C  | N.C            | В    |

| В    | N.C       | N.C  | 65  | 66 | 128  | CLK3 <b>*4</b> | В    |

- \*3 Rev2 より FPGA ピン#73 は I/O としてご使用いただけます。

- \*4 抵抗 R11 実装により FPGA ピン# 128 (CLK3) に接続可能

### 8.3 オンボードクロック

| 周波数    | NET LABEL | FPGA |

|--------|-----------|------|

| 40 MH  | CLK0      | 55   |

| 48 MHz | CLK1      | 56   |

12

### 9. 参考資料について

改訂資料やその他参考資料は、必要に応じて各製品の資料ページに公開致します。

http://www.hdl.co.jp/ftpdata/xcm-008/index.html

- 回路図

- ピンリスト

- 外形図

- パターン図

- ネットリスト …等

また下記サポートページも合わせてご活用ください。

http://www.hdl.co.jp/support\_c.html

### 10.付属資料

- 1. 基板外形図

- 2. 回路図(別紙)

### Spartan-3 ブレッドボード

XCM-008 シリーズ ユーザーズマニュアル

2005/08/08 Ver. 1.0 初版 (R1) 2006/04/25 Ver. 1.1 初版(A) (R1) 2007/04/26 Ver. 1.2 第 2 版 (R1) 2007/08/24 Ver. 1.3 第 3 版 (R1) 2007/12/14 Ver. 2.0 第 4 版 (Rev2) 2008/11/10 Ver. 2.1 第 5 版 (Rev2)

2010/05/24 Ver. 2.2

### 有限会社ヒューマンデータ

〒567-0034 大阪府茨木市中穂積 1-2-10 ジブラルタ生命茨木ビル

TEL 072-620-2002 FAX 072-620-2003

URL http://www.hdl.co.jp/