## Spartan-3AN 教育用ボード EDX-005 ユーザーズマニュアル

第2版

# 目次

| はじめに                               | 1  |

|------------------------------------|----|

| ご注意                                |    |

| 1. 製品の内容について                       | 2  |

| 2. 仕様                              |    |

| 3. 製品説明                            | 3  |

| 3.1. 各部の名称                         |    |

| 3.2. ブロック図                         |    |

| 3.3. 開発環境                          | 4  |

| 3.4. ダウンロードケーブル                    | 4  |

| 3.5. クロック                          |    |

| 3.6. 電源                            |    |

| 3.7. FPGA ヘコンフィギュレーション             | 4  |

| 3.8. JTAG コネクタ                     |    |

| 4. FPGA ピン割付表                      |    |

| 4.1. オンボードクロック                     |    |

| 4.2. 外部クロック                        |    |

| 4.3. USB 通信                        |    |

| 4.4. CNA                           |    |

| 4.5. CNB                           |    |

| 5. ドライバのインストール                     |    |

| 5.1. USB ドライバのインストール               |    |

| 5.2. USB ドライバのアンインストール             |    |

| 6. 各種ジャンパ設定                        |    |

| 6.1. 電源供給設定(JP4)                   |    |

| 6.2. コンフィギュレーションモード設定(JP5)         |    |

| 7. ディップスイッチの説明                     |    |

| 7.1. USB から FPGA ヘコンフィギュレーション      |    |

| 8. インシステムフラッシュメモリへの書込み             |    |

| 8.1. インシステム Flash プログラミングファイルの作成作成 |    |

| 8.2. インシステムフ Flash への書込み           |    |

| 8.3. インシステム Flash の Erase          |    |

| 9. 付属 CD-ROM の内容                   |    |

| 10. EDX-005 参考資料について               | 22 |

| 11 付居咨判                            | 22 |

#### はじめに

この度は、FPGA トレーナ EDX-005 をお買い上げいただきまして、誠にありがとうございます。

XILINX 社対応 FPGA トレーナ EDX-005 は、USB インタフェースをもつPCに接続し、XILINX 社の開発ソフト(ISE)などにより設計した回路を、USB 経由でコンフィグレーションできる学習用ボードです。

FPGA は、XILINX 社の高性能 FPGA である、Spartan-3AN を搭載しています。

USB インタフェースに FTDI 社の FT2232 を採用し、Ach をコンフィグレーション用に Bch をアプリケーション通信用に使用できます。アプリケーション通信は仮想 COM ポートドライバにより行うことができます。

EDX-005 は、専用コンフィギュレーションソフト(exe ファイル 1 本)により、bit ファイル さえあれば、XILINX 社の開発環境をインストールしていなくても FPGA へのコンフィギュレーションが行えますので、検査治具などにも便利にご利用いただけます。

コンフィギュレーション ROM、内部 SPI-ROM への書込みには、XILINX 社対応ダウンロードケーブルが別途必要になります。

#### ご注意

- 1 本製品には、民生用の一般電子部品が使用されています。 宇宙、航空、医療、原子力等、各種安全装置など人命、事故にかかわる 特別な品質、信頼性が要求される用途でのご使用はご遠慮ください。

- 2 水中、高湿度の場所での使用はご遠慮ください。

- 3 腐食性ガス、可燃性ガス等引火性のガスのあるところでの 使用はご遠慮ください。

- 4 基板表面に他の金属が接触した状態で電源を入れないでください。

- 5 定格を越える電源を加えないでください。

- 6 本書の内容は、改良のため将来予告なしに変更することがありますので、 ご了承願います。

- 7 本書の内容については万全の記して作成しましたが、万一誤りなど、お気 づきの点がございましたら、ご連絡をお願いいたします。

- 8 本製品の運用の結果につきましては、7. 項にかかわらず当社は責任を負いかねますので、ご了承願います。

- 9 本書に記載されている使用と異なる使用をされ、あるいは本書に記載されていない使用をされた場合の結果については、当社は責任を負いません。

- 10 本書および、回路図、サンプル回路などを無断で複写、引用、配布することはお断りいたします。

- 11 発煙や発火、異常な発熱があった場合はすぐに電源を切ってください。

- 12 ノイズの多い環境での動作は保障しかねますのでご了承ください。

- 13 静電気にご注意ください。

## 1. 製品の内容について

本パッケージには、以下のものが含まれています。万一、不足などがございましたら、 弊社宛にご連絡ください。

| FPGAトレーナ EDX-005 | 1 |

|------------------|---|

| 付属品              | 1 |

| USB ケーブル         | 1 |

| 付属 CD            | 1 |

| マニュアル(本書)        | 1 |

| ユーザ登録はがき         | 1 |

## 2. 仕様

| EDX-005                              |  |  |  |

|--------------------------------------|--|--|--|

| XC3S200AN-4FTG256C                   |  |  |  |

| DC 5V                                |  |  |  |

| N/A (詳細は FPGA データシートご参照)             |  |  |  |

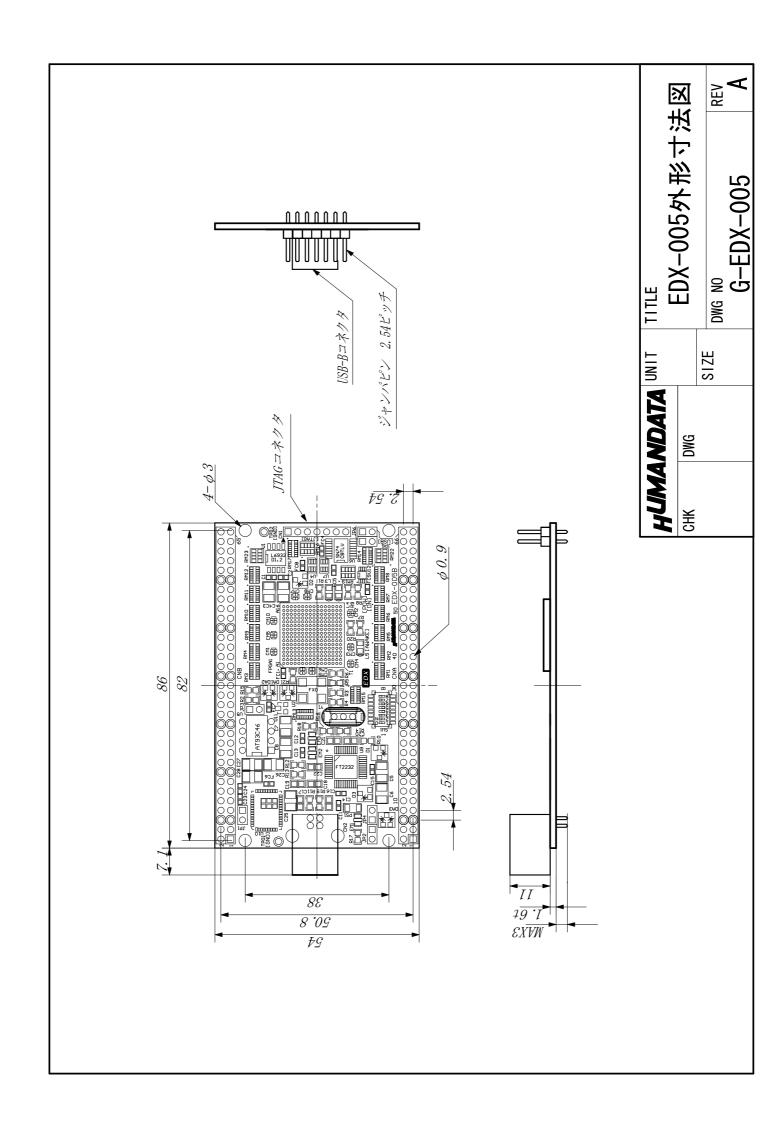

| 86 × 54 [mm]                         |  |  |  |

| 約 30g                                |  |  |  |

| 75 本                                 |  |  |  |

| 66 ピンスルーホール 0.9[mm φ]x2 組 2.54mm ピッチ |  |  |  |

| ガラスエポキシ 6 層基板 1.6t                   |  |  |  |

| オンボード 50MHz 6MHz 外部供給可能              |  |  |  |

| 内蔵 (240ms TYP)                       |  |  |  |

| DIP7 ピン ピンヘッダ 2.54mm ピッチ             |  |  |  |

| 3個(POWER-LED , DONE-LED , AWAKE-LED) |  |  |  |

| DIP80 ピンヘッダ 2 個(任意にカット可能)            |  |  |  |

| USB ケーブル(1.8m)                       |  |  |  |

|                                      |  |  |  |

### \* 互換品と変更になる場合がございます

EDX-005 第2版

## 3. 製品説明

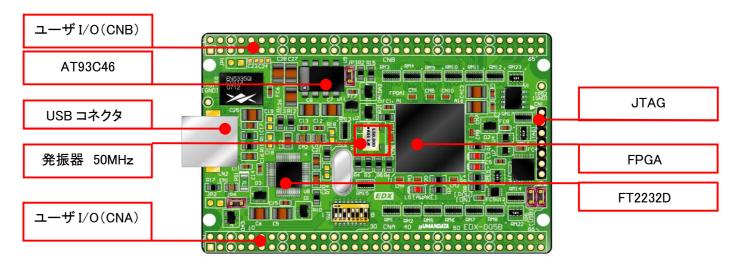

## 3.1. 各部の名称

部品面

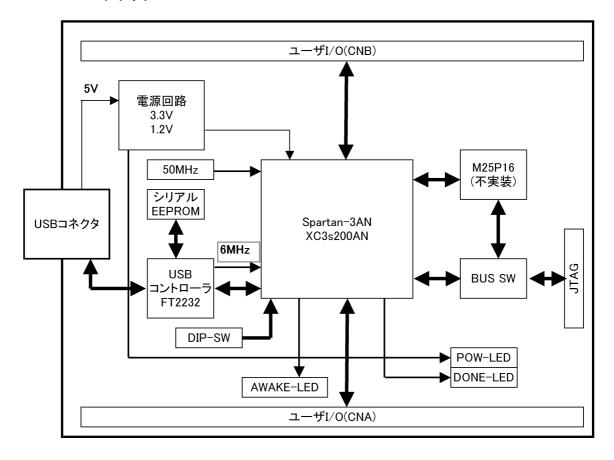

### 3.2. ブロック図

#### 3.3. 開発環境

FPGAの内部回路設計には、回路図エディタやHDL入力ツール、論理合成ツールが必要です。これらの開発ツールは、XILINX社が無償配布するISEにて可能です。使用する際には、インターネットによるライセンス登録が必要となります。

#### 3.4. ダウンロードケーブル

FPGA へのコンフィギュレーションには、専用のダウンロードケーブルを必要としません。 添付の USB ケーブルをご使用ください。

#### 注意

コンフィギュレーション ROM に ISP する際は XILINX 社対応ダウンロードケーブル が必要です。

## 3.5. クロック

クリスタルより 6MHz、発振器より 50MHzを FPGA に供給します。

#### 3.6. 電源

電源は USB から 5V が供給されます。FPGA の必要とする 3.3V、1.2V はオンボード レギュレータにより生成されます。

#### 5V は外部から供給することも可能です。(JP4 をオープンとしてください)

外部から電源を供給する場合 5.0V 電源は充分安定して、充分な余裕のあるものを ご用意ください。

外部から電源を供給する場合は、CNA、CNB から供給してください。

いずれも 5.0V を超えることはできません。

詳しくは FPGA のデータシートや回路図などを参照してください。また電源の立ち上がりは単調増加である必要があります。良質の電源を使用するようにしてください。

#### 3.7. FPGA ヘコンフィギュレーション

FTDI 社提供のダイレクトドライバをインストールすることで、USB 経由で FPGA にコンフィギュレーションすることができます。

コンフィギュレーションが終了し、DONE 信号が H になると、赤色 LED(L4)が点灯します。

## 3.8. JTAG コネクタ

FPGA へのコンフィギュレーション及び 内部マスタ SPI Flash モードに使用します。 ピン配置は次表のとおりです。

CN1

| 回路図上信号名 | ダウンロードケー<br>ブル信号名 | ピン番号 | ピン番号 | ダウンロードケー<br>ブル信号名 | 回路図上信号名 |

|---------|-------------------|------|------|-------------------|---------|

| XTCK    | TCK               | 1    | 2    | GND               | GND     |

| XTDO    | TDO               | 3    | 4    | VCC(3.3V)         | V33A    |

| XTMS    | TMS               | 5    | 6    | _                 | _       |

| _       | _                 | 7    | 8    | _                 | -       |

| XTDI    | TDI               | 9    | 10   | GND               | GND     |

弊社製ダウンロードケーブル XC3 や XILINX 社の純正ケーブルなどを用いることができます。

#### 使用例

注意

<u>ダウンロードケーブルを接続する場合、誤差しなどにご注意ください</u>

## 4. FPGA ピン割付表

## 4.1. オンボードクロック

| クロック  | NET LABEL | FPGA ピン# |

|-------|-----------|----------|

| 50MHz | GCLK0     | C10,D9   |

| 50MHz | GCLK1     | A9,C9    |

| 50MHz | GCLK2     | R7,T7    |

| 50MHz | GCLK3     | P8,T8    |

| 6MHz  | CLK-6M    | K14,15   |

## 4.2. 外部クロック

| コネクタピン NO | NET LABEL | FPGAピン# |

|-----------|-----------|---------|

| CNA-65    | CLKAP     | N9,P9   |

| CNA-66    | CLKAN     | T9,R9   |

| CNB-65    | CLKBP     | A8,B8   |

| CNB-66    | CLKBN     | C8,D8   |

## 4.3. USB **通信**

| NET LABEL | 方向  | FPGA ピン# |

|-----------|-----|----------|

| TXDB      | IN  | J16      |

| RXDB      | OUT | K16      |

| RTSB      | IN  | H14      |

| CTSB      | OUT | J14      |

6

EDX-005 第2版

## 4.4. CNA

| BANK | NET LABEL       | FPGA ピン# | CNA | ピン# | FPGA ピン# | NET LABEL       | BANK |

|------|-----------------|----------|-----|-----|----------|-----------------|------|

|      |                 | 3.3V     | 1   | 2   | 3.3V     |                 |      |

|      |                 | 5V       | 3   | 4   | 5V       |                 |      |

|      |                 | GND      | 5   | 6   | GND      |                 |      |

|      | IOA0            | G2       | 7   | 8   | H1       | IOA1            |      |

|      | IOA2            | Н3       | 9   | 10  | J3       | IOA3            |      |

|      | IOA4            | J1       | 11  | 12  | J2       | IOA5            |      |

|      | IOA6            | K1       | 13  | 14  | K3       | IOA7            |      |

|      |                 | GND      | 15  | 16  | GND      |                 |      |

|      | IOA8            | N2       | 17  | 18  | P1       | IOA9            |      |

|      | IOA10           | P2       | 19  | 20  | R1       | IOA11           |      |

|      | IOA12           | M1       | 21  | 22  | N1       | IOA13           |      |

|      | IOA14           | L1       | 23  | 24  | L2       | IOA15           |      |

|      |                 | GND      | 25  | 26  | GND      |                 |      |

|      | IOA16           | K4       | 27  | 28  | L3       | IOA17           |      |

|      | IOA18           | М3       | 29  | 30  | L4       | IOA19           |      |

|      | IOA20           | M4       | 31  | 32  | N3       | IOA21           |      |

|      | IOA22           | J4       | 33  | 34  | J6       | IOA23           |      |

|      |                 | GND      | 35  | 36  | GND      |                 |      |

|      | IOA24           | N7       | 37  | 38  | P6       | IOA25           |      |

|      | IOA26           | N8       | 39  | 40  | P7       | IOA27           |      |

|      | IOA28           | G3       | 41  | 42  | H4       | IOA29           |      |

|      | IOA30           | H6       | 43  | 44  | H5       | IOA31           |      |

|      |                 | GND      | 45  | 46  | GND      |                 |      |

|      | IOA32           | T4       | 47  | 48  | R5       | IOA33           |      |

|      | IOA34           | T5       | 49  | 50  | T6       | IOA35           |      |

|      | IOA36           | M10      | 51  | 52  | N10      | IOA37           |      |

|      | IOA38           | P11      | 53  | 54  | N11      | IOA39           |      |

|      |                 | GND      | 55  | 56  | GND      |                 |      |

|      | IOA40           | P13      | 57  | 58  | N12      | IOA41           |      |

|      | IOA42           | M13      | 59  | 60  | M14      | IOA43           |      |

|      | IOA44           | L13      | 61  | 62  | K13      | IOA45           |      |

|      | IOA46           | M15      | 63  | 64  | M16      | IOA47           |      |

|      | IOA48 <b>*1</b> | R13      | 65  | 66  | T13      | IOA49 <b>*2</b> |      |

<sup>\*1</sup> 抵抗アレイ(RM22)を介して FPGA ピン# N9,P9 (CLKAP) に接続

<sup>\*2</sup> 抵抗アレイ(RM22)を介して FPGA ピン# T9,R9 (CLKAN) に接続

### 4.5. CNB

| BANK | NET LABEL       | FPGA ピン# | CNB | ピン# | FPGA ピン# | NET LABEL       | BANK |

|------|-----------------|----------|-----|-----|----------|-----------------|------|

|      |                 | 3.3V     | 1   | 2   | 3.3V     |                 |      |

|      |                 | 5V       | 3   | 4   | 5V       |                 |      |

|      |                 | GND      | 5   | 6   | GND      |                 |      |

|      | IOB0            | В3       | 7   | 8   | A3       | IOB1            |      |

|      | IOB2            | B4       | 9   | 10  | A4       | IOB3            |      |

|      | IOB4            | E2       | 11  | 12  | E3       | IOB5            |      |

|      | IOB6            | C5       | 13  | 14  | A5       | IOB7            |      |

|      |                 | GND      | 15  | 16  | GND      |                 |      |

|      | IOB8            | В6       | 17  | 18  | A6       | IOB9            |      |

|      | IOB10           | F8       | 19  | 20  | E7       | IOB11           |      |

|      | IOB12           | D7       | 21  | 22  | C6       | IOB13           |      |

|      | IOB14           | A7       | 23  | 24  | C7       | IOB15           |      |

|      |                 | GND      | 25  | 26  | GND      |                 |      |

|      | IOB16           | B10      | 27  | 28  | A10      | IOB17           |      |

|      | IOB18           | E10      | 29  | 30  | D10      | IOB19           |      |

|      | IOB20           | C11      | 31  | 32  | A11      | IOB21           |      |

|      | IOB22           | A12      | 33  | 34  | B12      | IOB23           |      |

|      |                 | GND      | 35  | 36  | GND      |                 |      |

|      | IOB24           | A13      | 37  | 38  | A14      | IOB25           |      |

|      | IOB26           | D11      | 39  | 40  | C12      | IOB27           |      |

|      | IOB28           | D13      | 41  | 42  | C13      | IOB29           |      |

|      | IOB30           | E13      | 43  | 44  | D14      | IOB31           |      |

|      |                 | GND      | 45  | 46  | GND      |                 |      |

|      | IOB32           | B14      | 47  | 48  | B15      | IOB33           |      |

|      | IOB34           | C15      | 49  | 50  | C16      | IOB35           |      |

|      | IOB36           | D15      | 51  | 52  | D16      | IOB37           |      |

|      | IOB38           | E14      | 53  | 54  | F13      | IOB39           |      |

|      |                 | GND      | 55  | 56  | GND      |                 |      |

|      | IOB40           | F15      | 57  | 58  | E16      | IOB41           |      |

|      | IOB42           | G13      | 59  | 60  | F14      | IOB43           |      |

|      | IOB44           | H13      | 61  | 62  | G14      | IOB45           |      |

|      | IOB46           | F16      | 63  | 64  | G16      | IOB47           |      |

|      | IOB48 <b>*3</b> | H15      | 65  | 66  | H16      | IOB49 <b>*4</b> |      |

8

<sup>\*3</sup> 抵抗アレイ(RM23)を介して FPGA ピン# A8,B8 (CLKBP) に接続

<sup>\*4</sup> 抵抗アレイ(RM23)を介して FPGA ピン# C8,D8 (CLKBN) に接続

## 5. ドライバのインストール

#### 5.1. USB ドライバのインストール

FPGA へのコンフィギュレーションと、USB の通信実験の前には、FTDI 社の提供するドライバを PC にインストールする必要があります。本章で説明するインストール作業が完了後、FPGA へのコンフィギュレーションが可能になります。

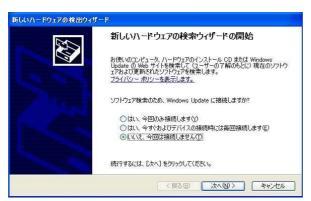

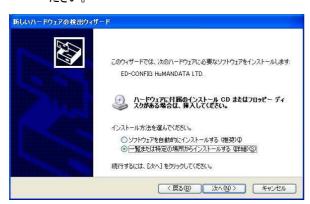

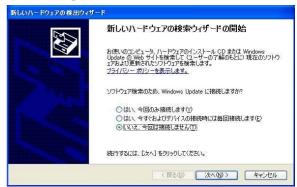

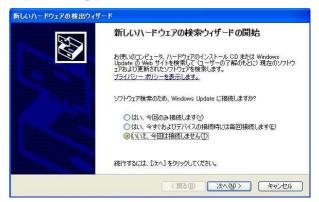

USB コネクタに付属 USB ケーブルを挿入すると「新しいハードウェア」が認識されます。次の手順に従ってインストール作業を完了してください。

Windows XP を例に作成しています。

いいえ、今回は接続しませんにチェックを入れ「次へ」をクリックしてください。

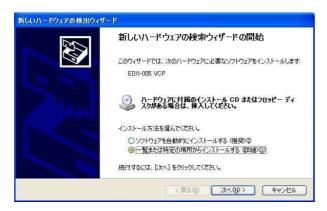

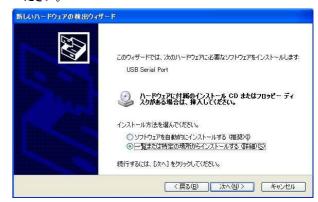

「一覧または特定の場所からインストールする」を選択し「次へ」をクリックしてください。

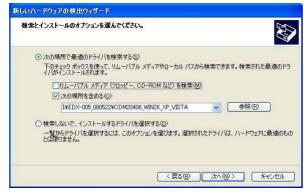

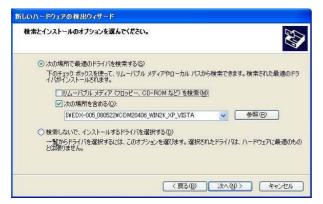

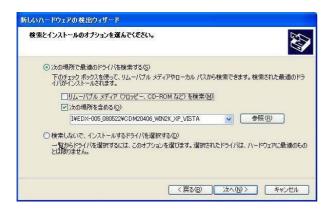

付属 CD 内の「CDM20406\_・・・」を選択し 「次へ」をクリックしてください。

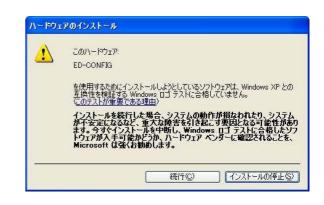

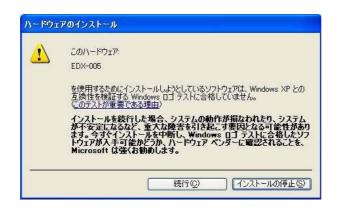

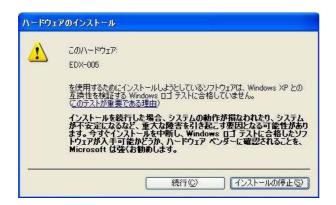

「続行」をクリックしてください。

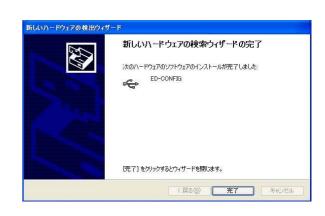

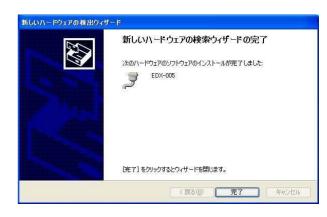

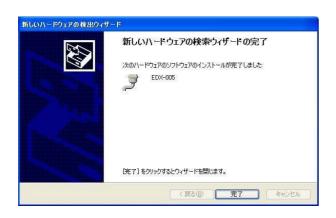

「完了」をクリックしてください。

いいえ、今回は接続しませんにチェックを入れ「次へ」をクリックしてください。

「一覧または特定の場所からインストールする」を選択し「次へ」をクリックしてください。

付属 CD 内の「CDM20406\_・・・」を選択し 「次へ」をクリックしてください。

「続行」をクリックしてください。

「完了」をクリックしてください。

いいえ、今回は接続しませんにチェックを入れ「次へ」をクリックしてください。

「一覧または特定の場所からインストールする」を選択し「次へ」をクリックしてください。

付属 CD 内の「CDM20406\_・・・」を選択し 「次へ」をクリックしてください。

「続行」をクリックしてください。

「完了」をクリックしてください。

これでドライバの組み込みが完了しました。

デバイスマネージャで確認すると次のようになっているはずです。

COM ポートの番号は、お客様の環境により異なります。COM ポートの番号を確認するためにも、一度ご確認を御願いします。

デバイスマネージャは、マイコンピュータのプロパティを選択し、ハードウエアタブからデバイスマネージャのボタンをクリックするか、マイコンピュータの管理から、デバイスマネージャをクリックするかのいずれかの方法で起動することができます。

新しいドライバが提供されたときは、 弊社サイトのサポートページの説明に 従ってください。

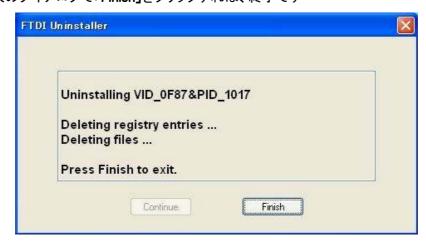

#### 5.2. USB ドライバのアンインストール

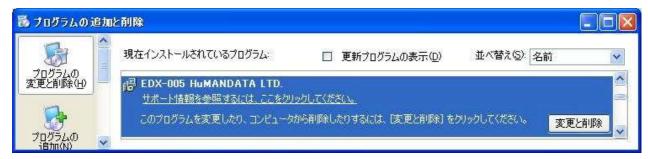

インストールした USB ドライバをアンインストールには、PC と EDX-005 を接続しない状態で「スタート」 - 「設定」 - 「コントロールパネル」 - 「アプリケーションの追加と削除」から「EDX-005 HuMANDATA LTD.」を選択し、「変更と削除」を実行してください。

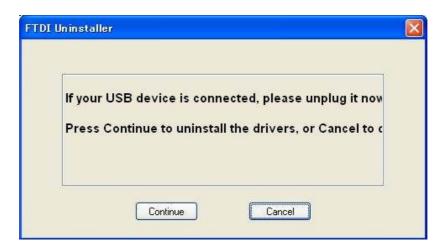

「Continue」をクリックします。

次のダイアログで「Finish」をクリックすれば、終了です

## 6. 各種ジャンパ設定

### 6.1. 電源供給設定(JP4)

JP4(ON): USB から 5V 供給

JP4(OFF): CNA、CNB から 5V 供給

## 6.2. コンフィギュレーションモード設定(JP5)

USB から FPGA ヘコンフィギュレーションを行う際、JP5 の設定が必要です。

JP5 — ターゲット 設定用

| JP5 | コンフィギュレーション方法 |

|-----|---------------|

| ON  | JTAG          |

| OFF | USB           |

USB からコンフィギュレーション(出荷時)

JP5 (OFF)

JTAG からコンフィギュレーション JP5 (ON)

大干

出荷時は USB からコンフィギュレーションの設定になっています。

## 7. ディップスイッチの説明

EDX-005 のディップスイッチ(SW4)は以下のように割り付けられています。 SW を **ON** で Low に固定されます。

| 番号  | S1     | S2   | S3          | S4   | S5     | S6       | S7    | S8            |

|-----|--------|------|-------------|------|--------|----------|-------|---------------|

| 記号  | X_PROG | X_M0 | X_M1        | X_M2 | VS2    | VS1      | VS0   | X_SUSPEND     |

| 出荷時 | OFF    | OFF  | OFF         | OFF  | OFF    | OFF      | OFF   | ON            |

| 説明  |        | +    | <br>ドセレクトピ: | ·    | SPI コン | フィギュレーショ | ョンモード | SUSPEND モード設定 |

|               | 内部マスタ SPI | マスタシリアル | マスタ SPI | マスタ BPIUP | JTAG    |

|---------------|-----------|---------|---------|-----------|---------|

| M[20]モードピンの設定 | <0:1:1>   | <0:0:0> | <0:0:1> | <0:1:0>   | <1:0:1> |

#### S1: ターゲット設定

OFF: JTAG(FPGA) ON: SPI-ROM

#### S2、S3、S4: モードセレクトピン

上記を参照し各コンフィギュレーションモードを設定してください。

#### S5、6、7: SPI コンフィギュレーションモード

EDX-005 は M25P80 を使用のため OFF 固定。(オプション)

#### S8: SUSPEND モード設定

詳しくは Spartan3-AN のデータシートをご覧ください。

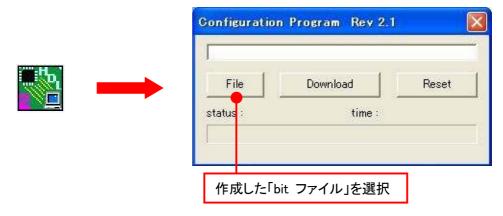

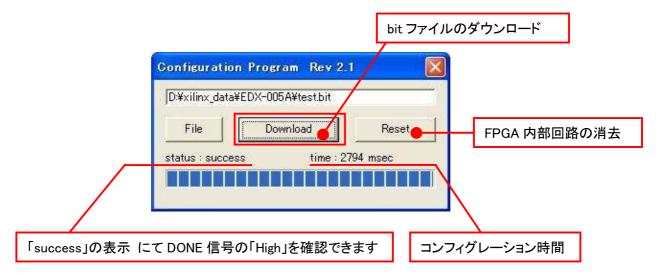

#### 7.1. USB から FPGA ヘコンフィギュレーション

付属 CD 内にある「BitCfg2.exe」を起動させると次のウィンドウが表示されます。

bit ファイルを選択し、Download をクリックします。

## 8. インシステムフラッシュメモリへの書込み

### 8.1. インシステム Flash プログラミングファイルの作成

この手順は、iMPACT を使用して、単体のビットストリームをインシステムFlashにプログラムする場合は不要です。

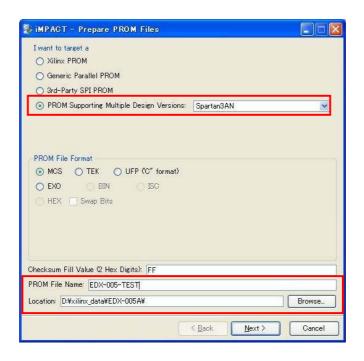

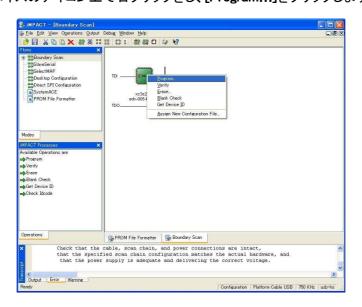

次に、下図のようにチェックを入れ、File Name と Location(保存先)を指定し <u>Next</u>>をクリックします。

EDX-005 第2版

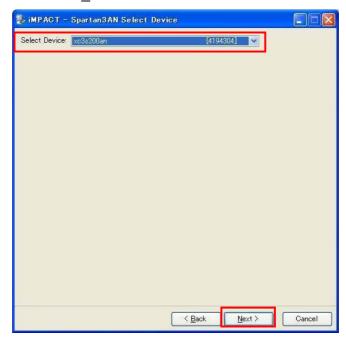

次に[xc3a200an]を選択し Next>をクリックします。

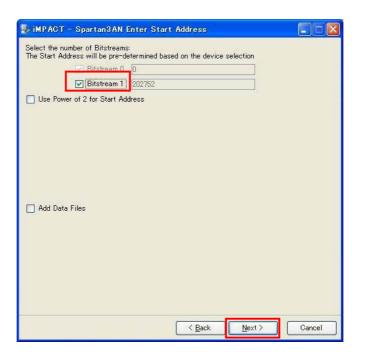

次に[Bitstream1]にチェックを入れ、Next>をクリックします。

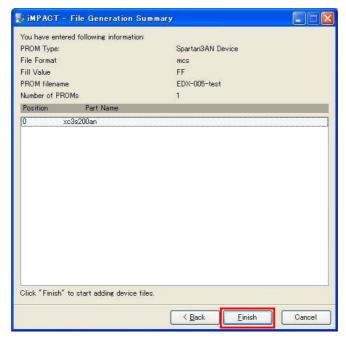

### Finishをクリックします。

#### OKをクリックします。

次に、作成した bit ファイルを選択します。

18

OK をクリックします。

次に、作成した bit ファイルを選択します。

OK をクリックします。

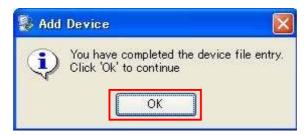

次に、iMPACT Processes のタブにある[Generate File...]をダブルクリックします。下記のように[PROM File Generation Succeeded]と表記されれば完了です。

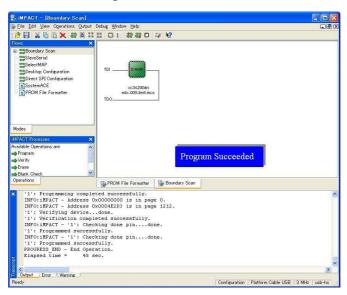

#### 8.2. インシステム Flash への書込み

EDX-005 にはインシステム Flash が使用可能です。

インシステム Flash に書込みする場合、ディップスイッチの設定が必要です。ディップスイッチを下記のように設定し iMPACT から書込みを行ってください。

|     | S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 |

|-----|----|----|----|----|----|----|----|----|

| ON  |    |    |    |    |    |    |    |    |

| OFF |    |    |    |    |    |    |    |    |

FPGA へのコンフィギュレーションは iMPACT により行います。

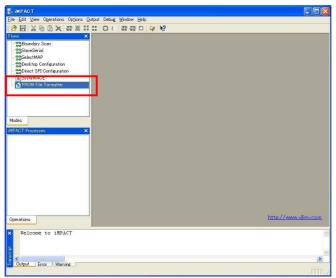

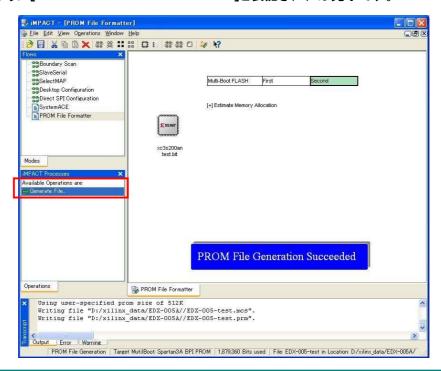

iMPACT を起動し[File]-[Initialize Chain]をクリックすると、FPGA が認識されます。

FGA に対して 6.1 項で作成した mcs ファイルを割り付けてください。

デバイスのアイコン上で右クリックをし、[Program...]をクリックします。

#### 書込みが成功すると、[Program Succeeded]と表記されます。

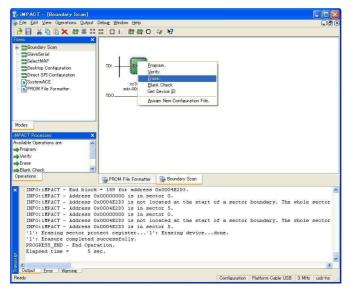

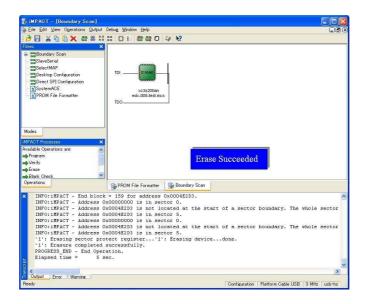

#### 8.3. インシステム Flash の Erase

デバイスのアイコン上で右クリックをし、[Erase...]をクリックします。

Erase が成功すると[Erase Succeeded]と表記されます。

## 9. 付属 CD-ROM の内容

「BitCfg21」

FPGA コンフィグレーションのためのソフトウェア

Visual C++ のソースコード

「DirectDriver」

USB ドライバ(FTDI 社ダイレクトドライバ)

「EDX-005」

[Document]

EDX-005 ユーザーマニュアル(カラー) EDX-005 回路図

最新のデータシートは、各社のホームページからダウンロードしてください。

XILINX 社のホームページhttp://www.XILINX.com/

FTDI 社のホームページhttp://www.ftdichip.com/

## 10. EDX-005 参考資料について

追加資料や参考資料がつくられた場合は

製品サポートページ

http://www.hdl.co.jp/support\_c.html にデータをアップロードすることにいたします。

## 11. 付属資料

- 1. 基板回路図(別紙)

- 2. 基板外形図

Spartan-3AN 教育用ボード EDX-005

ユーザーズマニュアル 2008/05/28 初版 2009/05/13 第 2 版

有限会社ヒューマンデータ 〒567-0034 大阪府茨木市中穂積1-2-10 ジブラルタ生命茨木ビル TEL 072-620-2002 FAX 072-620-2003 URL http://www.hdl.co.jp