2009/07/03-

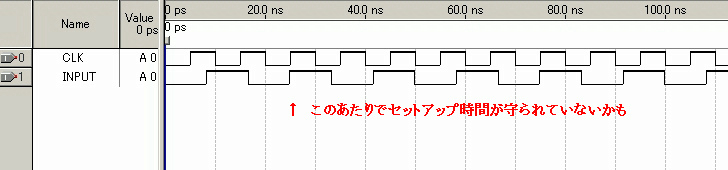

基本要素はフィリップフロップですので、クロックとデータの間にはセットアップ時間とホールド時間を守る必要があります。

うまく同期回路で設計できたとき、開発ツールのレポートでホールド時間は全てマイナスとなり、ホールド時間は考えなくて良くなります。

セットアップ時間やホールド時間は、ツールのレポートしたタイミングをすべて完璧に守る必要があります。

タイミング条件を守れないとき、メタステーブルというやっかいな現象が発生し、予想外の動作で悩まされることがあります。

メタステーブルの良い解説はこちらのリンクをご覧下さい。

アルテラ社のメタステビリティに関するアプリケーションノートはこちらのPDFをご覧下さい。

ザイリンクス社のメタステビリティに関するアプリケーションノートはこちらのPDFをご覧下さい。

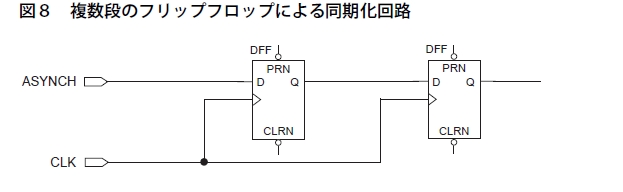

上記アプリケーションノートより

最近のFPGAでは内部クロックをPLLやDCMでてい倍し、相当高速のクロックで動作させることができるのはとてもありがたいことです。

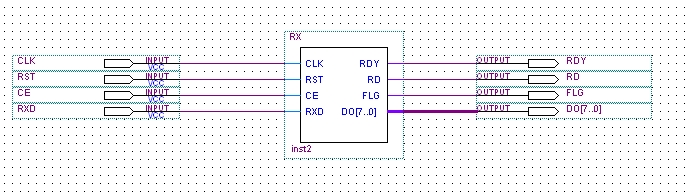

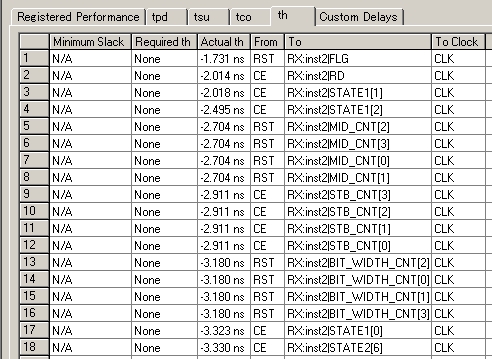

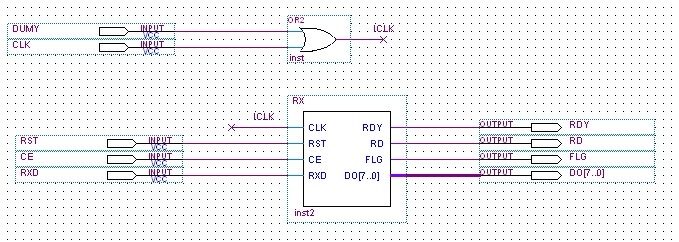

| とある回路と、そのタイミングレポート例です |

|

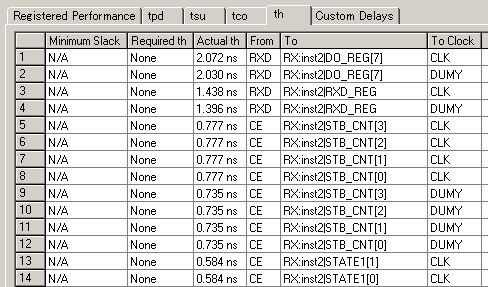

| ホールドは全てマイナスになっています。 |

GOOD GOOD |

| クロックをいじってわざと悪い回路にしてみると |

|

| ご覧のようにホールド条件にプラスが表れました |

BAD BAD |

(間違いなどありましたらご指摘をお願いします)