今後も実験を続けていきます。

2012/05/23 : システム構成、FPGA内部構造を追記しました

2012/05/22 : 公開しました

クリックして拡大 |

使用機器 | ||

| 機器名 | 型番 | メーカ | |

|---|---|---|---|

| Cyclone IV GX FPGAボード | ACM-024 | ヒューマンデータ | |

| 電源付きユニバーサル基板 | ZKB-105 | ヒューマンデータ | |

| アナログ カメラリンク ドライバー | ACLD-400 | 株式会社スタック様 | |

| 4.3インチ LCD タッチパネル | TRDB-LTM(ディスコン品) | Terasic 互換品としてUTL-021を販売しております  5"タッチパネル付きTFT-LCD 5"タッチパネル付きTFT-LCD |

|

| カラーCCDカメラ | TR-1300C | コロナ電業(株)様 | |

| ダウンロードケーブル | Terasic Blaster | Terasic社 | |

クリックして拡大

変換基板はアイテムラボ様のSOP28-1P27です。

コネクタは10226-2210PE(3M)を使用しています。

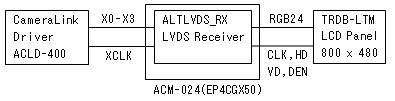

ACLD-400からのLVDS出力(データ x4, クロックx1)をFPGAで直接受信し、RGBデータを直接LCDに出力しています。

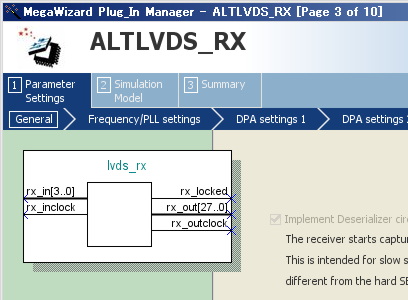

LVDS信号の受信に、ALTLVDSを使用しています

クリックして全体表示

クリックして全体表示データは4チャンネル(X0〜X3)なので"Number of Channels"には「4」を設定します

CameraLinkでは、1データレーンあたり1クロックで7bit転送します。"Deserialization Factor"には「7」を設定します

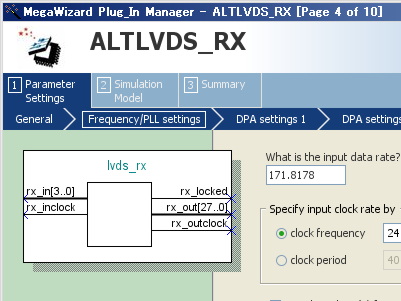

クリックして全体表示

クリックして全体表示ACLD-400からのクロック出力は、NTSCの場合24.5454MHzですので、"Clock Frequency"には24.55MHzを設定します

"Clock Frequency"に"Deserialication Factor"を掛けた171.8178を"Input Data Rate"に設定します

・6/1追記

コンパイルでタイミングエラーが発生し、画像表示が乱れることがありました。

PLLを外付けにすることで解消しています。

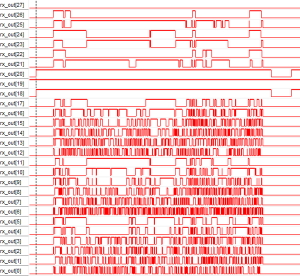

データ波形をSignalTapで取ってみました。水平同期信号の間にRGBのデータが取得できていることがわかります。

| ネット名 | 信号 | 意味 |

| rx_out[27] | Spare | 予備ビット |

| rx_out[20] | DVAL | フレームとラインが有効 |

| rx_out[19] | FVAL | フレームが有効(垂直同期信号) |

| rx_out[18] | LVAL | ラインが有効(水平同期信号) |

| rx_out[22:21],[5:0] | R[7:0] | 赤色輝度データ |

| rx_out[24:23],[11:6] | G[7:0] | 緑色輝度データ |

| rx_out[26:25],[17:12] | B[7:0] | 青色輝度データ |

クリックして拡大表示

当社では、通常、サンプル回路などのご提供は行っておりません。

間違いなど見つけられましたらぜひご指摘下さい。