こんなこともできるという例としてどうぞご覧下さい。

(画像はそれぞれクリックして拡大できます)

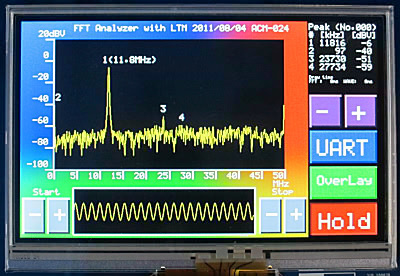

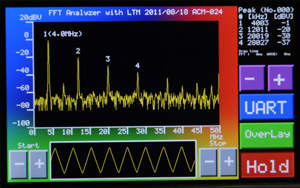

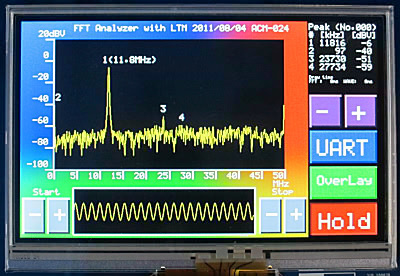

波形表示、4つまでのピーク検出機能、重ね書きモード、レンジ変更の機能を実装しています。

FFT処理は10.24uSec程度となっています。

A/Dのサンプリングレートは100MHz/16bit、1024サンプルで512ポイントという条件です。

2011/04/12:UTL-016を使用した写真を追加しました

2011/09/20:追記しました:「FPGA内部構成」

2011/09/15:とりあえずの完成型として、機能面などを追記しました

2011/07/28:途中経過を公開

XILINX Spartan-6(XCM-020)での同様の実験はこちらをご覧下さい。

クリックして拡大 |

使用機器 | ||

| Cyclone IV GX FPGAボード | ACM-024 | ヒューマンデータ | |

| SIF40 to SMA 変換基板 | ACC-010 | ヒューマンデータ | |

| A/D変換基板 | LTC2274評価キット | アナログ・デバイセズ(リニアテクノロジー) | |

| UTL-016で動作致します | ヒューマンデータ | ||

| マルチファンクションシンセサイザ(SG) | WF1965 | エヌエフ回路設計ブロック | |

| 4.3インチ LCD タッチパネル | TRDB-LTM(ディスコン品) | Terasic 互換品としてUTL-021を販売しております  5"タッチパネル付きTFT-LCD 5"タッチパネル付きTFT-LCD |

|

| ダウンロードケーブル | Terasic Blaster | Terasic | |

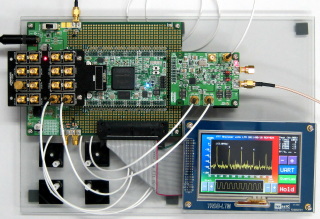

◆UTL-016を使用して動作

クリックして拡大

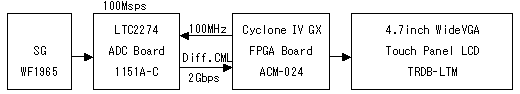

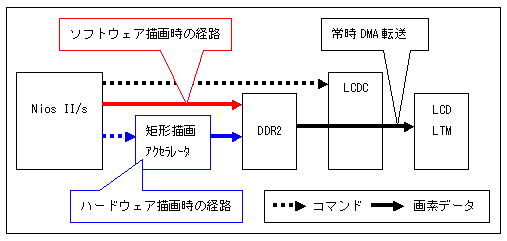

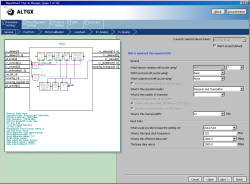

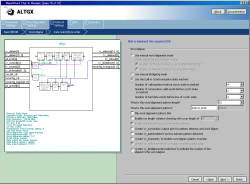

構成図は下図のようになります

信号発生器(SG)かからの出力をLTC2274でA/D変換し、データを8B10B変換されたシリアルデータとしてACM-024にて受信しています。

ACM-024からLTC2274には同期信号として100MHzを供給しています。

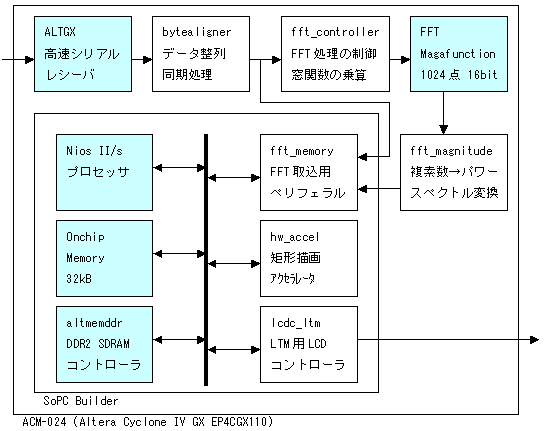

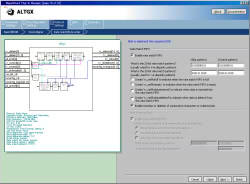

ALTGXにてLTC2274からのシリアル信号を受け、後段のbytealignerにて受信処理を行っています。

FFT解析前にデータ処理(窓関数)を行っており、解析出力データをスペクトル変換しています。FFTのIPはアルテラMegaFunctionのものを使用しています。データをLCDに表示するために、Nios Avalonバスから取り込めるよう、取り込み用ペリフェラルを設置しています。

LCDへの画素データの転送は、常時一定レートかつ高速(100MB/s)で行う必要があるため、LCDコントローラを作成し、DDR2メモリからDMA転送しています。また、描画を高速化するために、矩形塗りつぶし処理をハードウェアで行っています。

一本のスペクトルは、ある程度幅があり、頂点の前後2〜3点のデータも大きな値を持ちます。

単純にピーク値を数字の大きいほうから4つ求めると、複数のピーク値が一本のスペクトルの頂点と裾を示してしまいます。

このデモのピーク検出では極大点の検出(傾きが正から負に変わることを利用)を行い、極大値の大きいほうから4つをピーク値として表示しています。

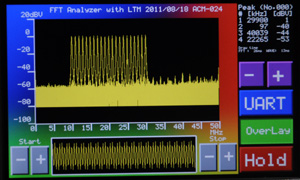

通常では背景を黒く塗りつぶすことで前回のスペクトルを消去しています。

重ね描きモードではこの消去作業とスペクトル上でのピーク表示を省くことでスペクトルを重ねて表示します。

消去作業が不要なので通常時よりも更新速度は速くなります。

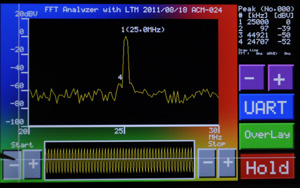

スペクトルの表示開始位置と終了位置をボタンで設定します。

画面のように、ボタンをタップすると凹状態に変化し、押されたことをわかりやすく示します。

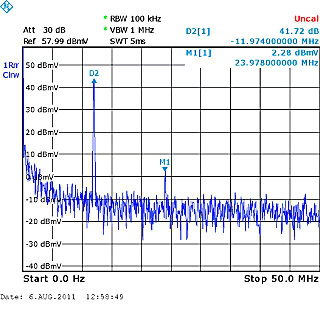

上の写真と同じ信号を6GHzスペックのスペアナでみると下図のようになります。

- 転送レート:2Gbps

- リファレンスクロック:125MHz(オンボード)

- ワードアライン:K28.5(-) → K28.7(-) に変更

LTC2274のFAM(Frame Alignment Monitor)を有効にし、Syncするタイミングを増やしました

- Rate Match FIFO:有効、Skip Pattern:K28.5 Controlパターン:K28.5

LTC2274は、16Bit 105Msps シリアル出力 A/D変換器です。

測定データは8B10Bエンコードされたシリアルデータで出力されますので、FPGAの高速シリアルI/F(HS Transceiver)と容易に接続できます。

文字フォントについては、こちらのフォントを活用させていただきました。(ありがとうございました)

当社では、通常、サンプル回路などのご提供は行っておりませんが、本アプリケーションについてはご提供が可能かどうかを検討しております。

間違いなど見つけられましたらぜひご指摘下さい。