ALTERA Cyclone IV 差動ターミネーション実験

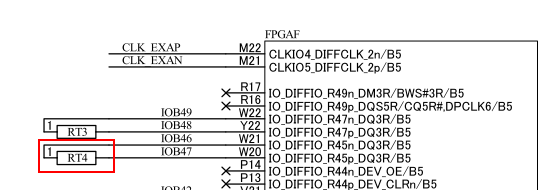

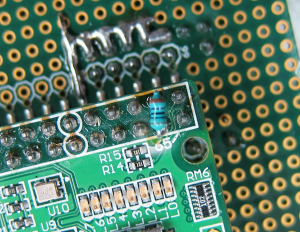

ALTERA社のCyclone IV FPGAボード、ACM-024を使用しています。

◆観測条件

今回の観測には、以下のものを使用しています。今回は80MHzのLVDS信号を受信しました。| 使用機材 | 型番 | 画像 | メーカ | 備考 |

|---|---|---|---|---|

| Cyclone IV FPGAボード | ACM-024 | HuMANDATA | ZKB-105を使用 | |

| 信号発生器 | CG635 |  |

Stanford Research Systems, Inc. | 80MHz、LVDS出力 |

| オシロスコープ | DPO4054 | - | Tektronix | 250MHz帯域制限 |

| FETプローブ | P6243 | - | Tektronix |

◆観測結果

観測結果をお示しします。観測はオンボードターミネーション抵抗用フットプリント:RT4をプロービングしています。

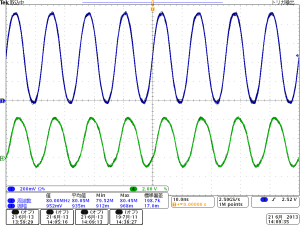

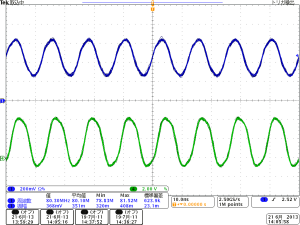

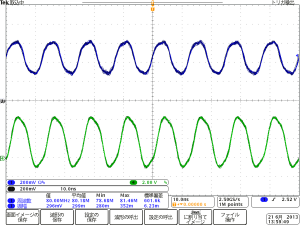

上波形(青色)がオンボード終端抵抗(RT4)位置で観測した波形です。下波形(緑色)はFPGAで受けた波形をシングルエンド出力したものです。

| 波形 | ターミネーション(100Ω) |

|---|---|

|

なし |

|

コネクタ クリックして拡大 |

|

RT4 |

◆まとめ

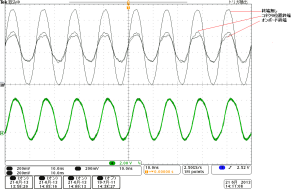

波形を同一画面にまとめたものをお示しします。

コネクタ位置での終端であっても、オンボード抵抗位置での終端と遜色ない結果が得られました。

間違いなど見つけられましたらぜひご指摘下さい。