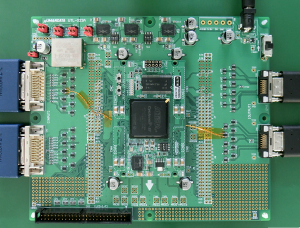

FPGAボードにはCyclone IV E搭載FPGAボードACM-204を使用しています。また、デモンストレーションとして、取り込んだ画像の一部をLCDに出力しています。

開発にはQuartus II Ver11.1 SP2を使用しています。

◆機器構成

クリックして拡大 |

使用機器 | ||

| 機器名 | 型番 | メーカ | |

|---|---|---|---|

| カメラリンク実験用ボード | UTL-023 | ヒューマンデータ | |

| Cyclone IV E FPGAボード | ACM-204 | ヒューマンデータ | |

| タッチパネル付き5"カラーLCDモジュール | UTL-021 | ヒューマンデータ | |

| カメラ | ACEシリーズ acA2040-180km |

BASLER社 | |

| CameraLinkケーブル(PoCL) | 199745A-07 | National Instruments | |

| CameraLinkケーブル | 1MF26-L560-00C-500 | 3M | |

| ダウンロードケーブル | Terasic Blaster | Terasic社 | |

◆UTL-023 (カメラリンク実験用ボード(CameraLink入出力ボード))

UTL-023 はヒューマンデータのカメラリンク実験用ボードです。入力コネクタにはMDRコネクタを搭載しています(左側)。出力クコネクタにはSDRコネクタを搭載しています(右側)。全てのカメラリンク信号線にはESD保護素子を実装しています。

カメラリンク入力コネクタからカメラへの12V電源出力(PoCL)はジャンパでオンオフを切り替え可能です。 (最大出力:6W)

基板下部の50ピンヘッダからはタッチパネル付き5"カラーLCDモジュール(UTL-021)が接続可能です。

クリックして拡大

◆接続したカメラ

BASLER社のACEシリーズacA2040-180kmを接続しました。 (画像はメーカサイトより引用しました)

(画像はメーカサイトより引用しました)| カラー | 画素数 [pixel] | FPS | I/F構成 | データbit数 | クロック [MHz] | 電源[V] | レンズ |

| モノクロ | 2048 x 2048 | 180 fps | Base/Medium/Full | 10/12bit | 32.5/48/65/82 | 12V (PoCL またはコネクタ入力) | Cマウント |

この例では、Full Configuration, 8Tap, 10bit, 32.5MHz の設定で実験を行っています。

動作モードはシリアルI/Fから設定しています。設定にはNiosIIのシリアル通信を使用しました。下記の設定を行っています。

| レジスタ | 設定項目 | 設定値 |

| Device Information | CL Pixel Clock | CL Clock 32.5 |

| Image Format | Sensor Digitization Taps | 8Tap |

| Image Format | Sensor Bit Depth | 10bit |

| Image Format | Pixel Format | Mono 10 |

| User Set Control | Default Set Selector | User 3 |

◆システム構成

全体の構成は下図のようになっています。CameraLinkの信号をACM-204で取込み、リクロックしてから出力しています。カメラからのクロックは32MHzで設計しています。また、デモンストレーションとして、中継するデータの一部はLCDに表示されます。※QusrtusII 11.1 SP2にて開発しています

カメラからの画像データは左側のUTL-023で一度中継された後、右側のUTL-023で受信されています。何段でも接続できるようになっています。

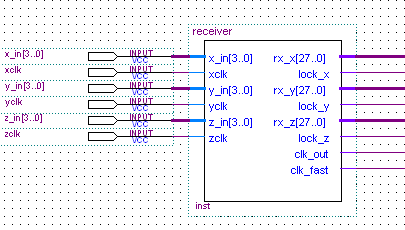

◆LVDSレシーバの設定

LVDSレシーバでは、X,Y,Zそれぞれの信号を各々のクロックを使って受信しています。ですので受信用にPLLを3つ使用しています。下図はLVDSレシーバを3つまとめたブロックの回路図ライブラリです。X,Y,Zそれぞれのシリアル信号がデシリアライズされたパラレル信号(28bit)が出力されます。lock_x,y,z信号はPLLのLock信号です。

"clk_out"には後段のユーザーロジックに使用するため、入力と同じクロック(32.5MHz)が出力されています。"clk_fast"はLVDSトランシーバで使用されます。

クリックして拡大

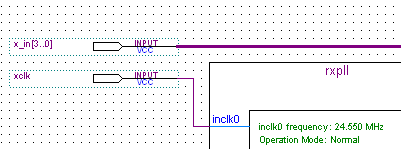

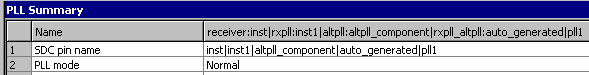

LVDSレシーバ(ALTLVDS_RX)は外部PLL設定で使用しています。これはLVDSトランシーバとクロックを共有するためです。また、細かい遅延値の設定も可能です。下の画像はXデータの受信部です。

クリックして拡大

PLLの設定値は、ALTLVDS_RXのMegaWizard画面より指定されますので、それに従います。

"rx_inclock"にはデータレートの半分ですので "32.5*7/2 MHz"を、"rx_syncclock"には"rx_inclock"の1/7、つまり"32.5/2MHz"を供給します。同様に"rx_readclock"は"32.5MHz"となります。

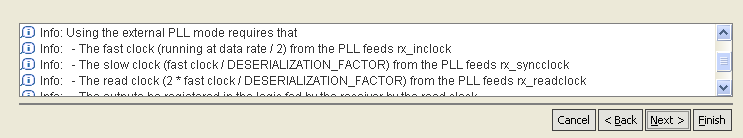

クリックして拡大

PLLブロック図の入力クロック値が24.55MHzとなっていますが、正常に動作します。これはPLLのLock周波数範囲内に32.5MHzが含まれるためです。

クリックして拡大

◆LVDSトランスミッタの設定

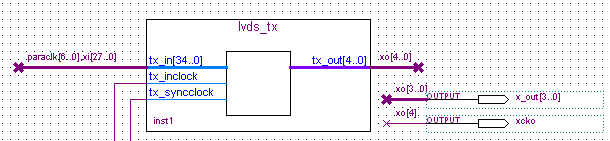

LVDSトランスミッタ(ALTLVDS_TX)は、送信する画像データに、クロックもデータとして合わせてシリアライズしています。出力数は5チャンネルになります。

"tx_inclock"にはレシーバブロックから"32.5*7/2MHz"が供給されています。"tx_syncclock"はレシーバと同様に"32.5MHz"です。

クリックして拡大

クリックして拡大◆LCD表示器への表示

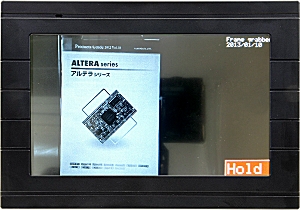

中継するデータを観察するためにタッチパネル付きカラーLCDモジュール (UTL-021) への表示を行いました。画像データ8Tapのうち、間引きした2TapのデータをLCDに表示しています。そのため表示される画像は約1/4に圧縮されたものになっています。

カメラからの全画素データ(2048x2048)に対し、1/4の画像データ(512x512)を取込み、LCDの縦サイズに合わせて、480x480サイズで表示しています。

(この画面ははめ込み合成です)

間違いなど見つけられましたらぜひご指摘下さい。