丂

丂 Verilog-HDL 僒儞僾儖夞楬

2002/09/12(峏怴擔 2021擭05寧11擔)

仠巇條

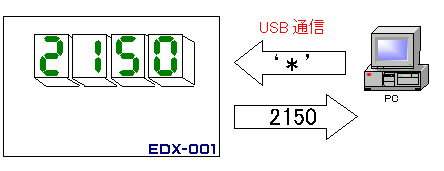

EDX-001偺7僙僌儊儞僩LED4偮傪巊偄丆俀係帪娫帪寁傪嶌惉偟丆偙偺帪娫傪USB働乕僽儖偵偰俹俠偱庴怣偟傑偡丏俹俠偐傜乽仏乿(0x2A)傪憲怣偡傞偙偲偱丆乽俀侾丗俆侽乿偱偁傟偽丆乽21乿[50]偺俀僶僀僩傪曉怣偡傞夞楬偱偡丏墴偟儃僞儞僗僀僢僠俠偲俢傪墴偡偙偲偱丆帪偲暘傪曄峏偱偒傞傛偆偵偟傑偡丏侾暘傪侾昩偲偡傞偙偲偱丆帪娫偺曄壔傪傢偐傝傗偡偄傛偆偵偟傑偡丏

|

仠摦嶌妋擣

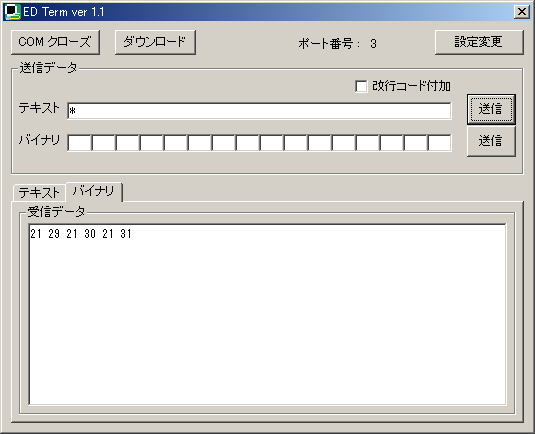

僶僀僫儕僨乕僞偺庴怣傪妋擣偡傞偨傔偵丆倁俛偺僒儞僾儖捠怣僜僼僩偱偁傞俤俢 俿俤俼俵傪棙梡偟傑偡丏僥僉僗僩偲偟偰丆'*'傪憲怣偟傑偡丏僞僽傪乽僶僀僫儕乿偵曄峏偟偰壓偝偄丏'*' 傪俁夞墴偡偲丆庴怣僨乕僞偵偼 21 29 21 30 21 31 (俇僶僀僩)偲庴怣偟傑偟偨丏傑偨丆俤俢倃亅侽侽侾偺俈僙僌儊儞僩俴俤俢偵偼俀侾帪俁侾偲側偭偰偄傑偡丏

仠夞楬偺奣梫

| clock_top | 僩僢僾儌僕儏乕儖 | ||

| clk_div | 暘廃夞楬丏侾昩偺僋儘僢僋僀僱乕僽儖傪惗惉 | ||

| clock | 侽侽丗侽侽 偐傜 俀係丗俆俋丂傑偱傪暘廃夞楬偺俠俤傑偨偼僗僀僢僠偵傛偭偰丆僇僂儞僩傾僢僾偡傞丏 | ||

| diff_pls | 乽俫乿偺忬懺傪侾廃婜偵偡傞丏旝暘夞楬偺傛偆側傕偺丏 | ||

| rem_chat | 墴偟儃僞儞僗僀僢僠偺僠儍僞儕儞僌傪偲傞 | ||

| reply | PC偐傜偺乽仏乿傪敾暿偟丆帪偲暘傪曉怣偡傞 | ||

| usb_arbiter | USB偺挷掆夞楬 | ||

| seg_ctl | 俈僙僌儊儞僩僐儞僩儘乕儔偺僩僢僾 | ||

| SEG_CNT | 僙僌儊儞僩僇僂儞僞 | ||

| SEG_DEC | 僙僌儊儞僩僨僐乕僟 | ||

| SEG_MUX | 僙僌儊儞僩偺僙儗僋僞 (4偮偺偆偪侾偮傪慖傇 ) | ||

仠僟僂儞儘乕僪

| 僜乕僗僼傽僀儖 (UCF僼傽僀儖傪娷傓) | EDXSPLvrg01_src.zip |

| ISE偺僾儘僕僃僋僩 | EDXSPLvrg01.zip |

僒儞僾儖 嘦丂乣嶌惉拞乣