サンプル回路

2002/07/18(更新日 2021年05月11日)

| サンプル回路 1 | ダウンロード : EDX_SPL1 |

7セグLEDを2つ使用する。"00"から"59"までカウントアップする回路。  |

|

| モジュール名 | ||

| 1 | EDXSPL1_TOP | トップモジュール |

| 2 | CLK60 | 10秒桁と1秒桁のカウンタ |

| 3 | CLKDIV | 約1秒を生成 |

| 4 | SEG_CTL | 以下のモジュールを接続 ※7セグへの出力にD-FFをつけていないので、ハザードが生じます |

| 5 | SEG_CNT | ダイナミック点灯のカウンタ 次のgeneric文は点灯させる7セグメントLEDの個数 generic ( MAX_SEG : integer := 2 ); |

| 6 | SEG_DECODER | セグメントデータ(SG) のデコーダ |

| 7 | SEG_MUX | ダイナミック点灯のため、どの7セグを表示させるか決定 |

| サンプル回路 2 | ダウンロード : EDX_SPL2 |

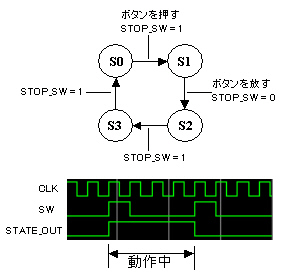

サンプル回路1にストップとリセットを追加する。 1.PSW0を押すと、表示を維持。再度押すと、再び動作する。 2.PSW1を押すと、"00"に戻す。 |

|

▼ボタンを押した状態を連続で認識しないように記述したステートマシン

|

when S0 => |

| モジュール名 | ||

| 1 | EDXSPL2_TOP | トップモジュール |

| 2 | CLK60 | 10秒桁と1秒桁のカウンタに停止と初期化の条件を加えたもの |

| 3 | CLKDIV | 入力パラメータ変更により、約1Hzと約100kHzを生成 |

| 4 | CHATTERING | チャタリングを取除く |

| 5 | STATE_MACHINE | "停止"と"開始"の2つの状態を定義 |

| 4 | SEG_CTL | 7セグ表示部分はサンプル回路1と同じ |

| サンプル回路 3 | ダウンロード : EDX_SPL3 |

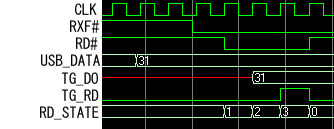

パソコンから仮想COMポート等を利用して、アスキー文字を送信し、ボードが受信したデータをそのままPCに送り返すエコー回路。 |

|

▼USB調停回路のステートマシン

| --USB FIFO から読込み case RD_STATE is when S0 => --書込み中ではなく、ターゲットの準備もOK if( RXF_REG='1' and TG_READY='1' and WR_STATE="00") then RD_N <= '0'; RD_STATE <= S1; else RD_STATE <= S0; end if; when S1 => TG_DO <= USB_DATA; --データ取り込み RD_STATE <= S2; when S2 => RD_N <= '1'; TG_RD <= '1'; RD_STATE <= S3; when S3 => TG_RD <= '0'; --ターゲットのモジュールに読込み信号 RD_STATE <= S0; when others => RD_STATE <= S0; end case; |

--USB FIFO に書込み case WR_STATE is when S0 => --ターゲットからの書込み信号を受ける if( TG_WR='1') then USB_DATA_REG <= TG_DI; WR_STATE <= S1; else WR_STATE <= S0; end if; when S1 => --USBへの書込みが可能かつ、読込み中ではない if( TXE_REG='1' and RD_STATE="00") then WR <= '1'; DIR <='1'; WR_STATE <= S2; else WR_STATE <= S1; end if; when S2 => WR <= '0'; --書込み DIR <= '1'; --バスをUSB側 WR_STATE <= S3; when S3 => WR <= '1'; --書込み終了 DIR <= '0'; --バスをFPGA側 WR_STATE <= S0; when others => WR_STATE <= S0; end case; |

|

|

| モジュール名 | ||

| 1 | EDXSPL3_TOP | トップモジュール |

| 2 | USB_ARBITER | USBの調停回路 |

| サンプル回路 4 | ダウンロード : EDX_SPL4 |

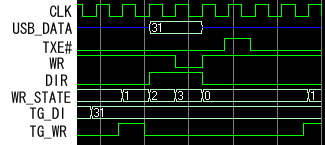

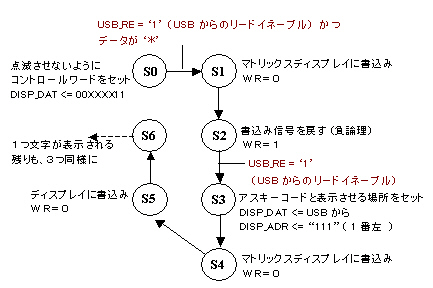

サンプル回路3を利用。USBから’*’を認識し、4文字のアスキー文字を表示させる |

|

▼ドットマトリックスディスプレイへの表示手順

|

-- AST はアスタリスクで頭だし -- S0 の DISP_DAT と DISP_ADR は点滅させないため when S0 => if( USB_RE='1' and USB_DAT=AST ) then DISP_DAT <= "00XXXX11"; DISP_ADR <= "0XX"; DISP_WR_N <= '1'; STATE <= S1; else STATE <= S0; end if; when S1 => DISP_WR_N <= '0'; STATE <= S2; when S2 => DISP_WR_N <= '1'; STATE <= S3; |

| モジュール名 | ||

| 1 | EDXSPL4_TOP | トップモジュール |

| 2 | USB_ARBITER | USB調停回路 |

| 3 | PD_LED | LEDディスプレイ制御 |