ダウンロード手順 ISE Foundation の使い方

2002/07/18(更新日 2021年05月11日)

| 1. Project Navigator の起動 |

| 2. 新規プロジェクトの作成 |

| 3. 新規 VHDL ソースファイルの作成 |

| 4. 新規テストベンチの作成 |

| 5. シミュレーションの実行 |

| 6. ピン固定ファイルの作成 |

| 7. 論理合成・配置配線の実行 |

| 8. ビットファイルの作成 |

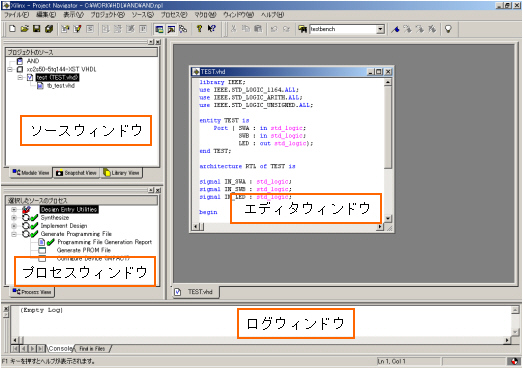

1 Project Navigator の起動

スタートメニューから [ スタート ]→[プログラム]→[ ザイリンクス ISE ]→[ Project Navigator ] を起動します。

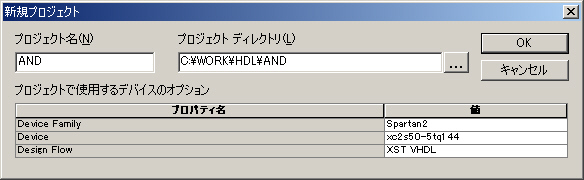

2 新規プロジェクトの作成

[ ファイル ]→[ 新規プロジェクト ]を選択。以下のようなダイアログが表示されます。Device Familyは [ Spartan 2 ]、Deviceは [ xc2s100-5tq144 ] を選択します。Design Flowには [ XST VHDL ]、[ XST Verilog ] を選択してください。ここでは VHDL を使用します。また、画像には [ xc2s50-5tq144 ] となっていますが、[ xc2s100-5tq144 ] を選んでください。

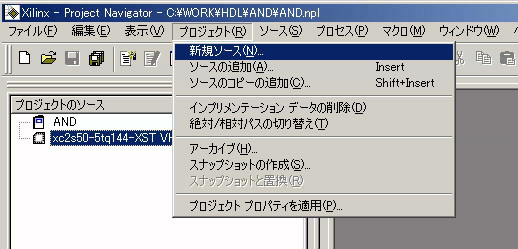

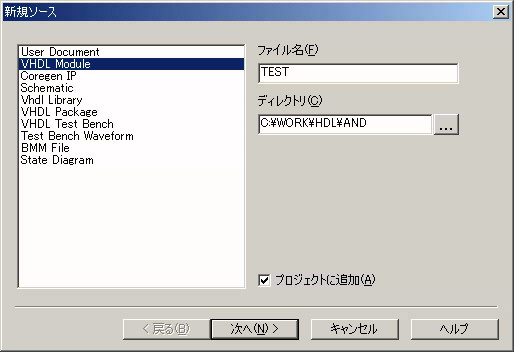

3 新規VHDLソースファイルの作成

[ プロジェクト ]→[ 新規ソース ] を選択します。

VHDLモジュールとして、ファイル名とディレクトリを指定します。

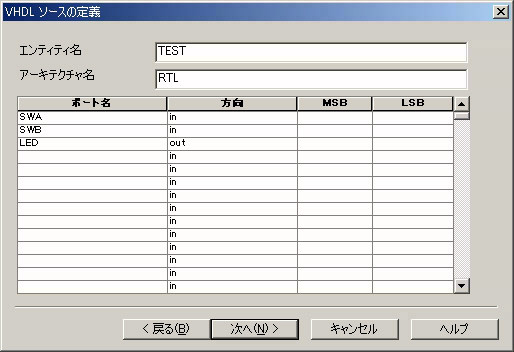

ポート名や方向を入力すると、VHDLソースの雛型を自動で生成してくれます。

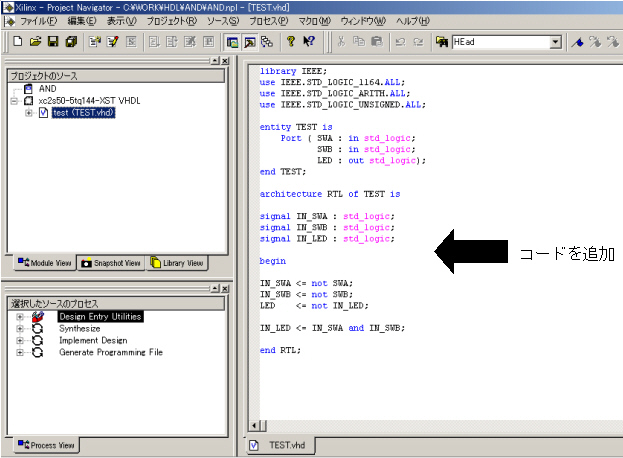

作成された雛型のソースにコードを追加します。

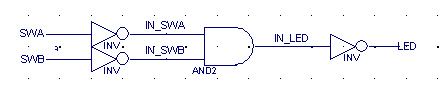

記述したコードは以下のような回路です。押しボタンスイッチは、押すとLowであり、汎用LEDはLowで点灯するので、以下のようにインバータを挿入した回路になります。厳密には、ハイインピーダンス、オープンドレインにて完全に消灯します。

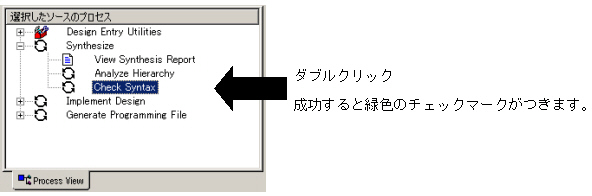

プロセスウィンドウの [ Synthesize ]→[ Check Syntax ] をダブルクリックし、VHDLの文法チェックを行います。

4 新規テストベンチの作成

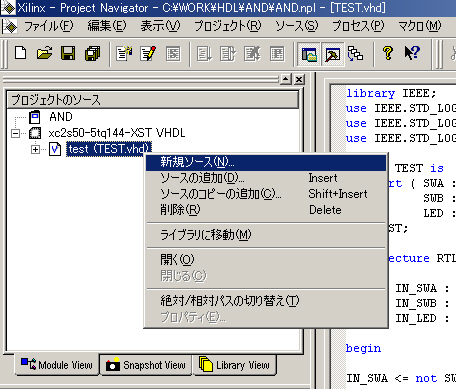

記述したVHDLファイルのシミュレーションに必要なテストベンチを作成します。VHDLソースをクリックして右ボタンを押すと以下のような画面になります。 [ 新規ソース ] を選択します。

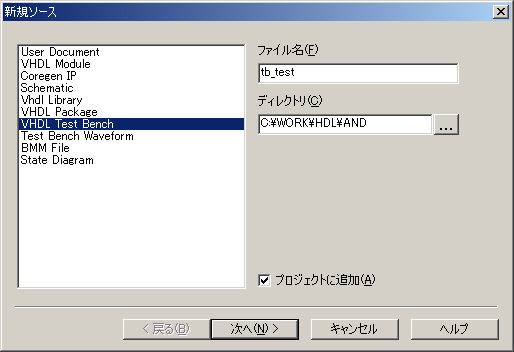

ダイアログには [ VHDL Test Bench ] を選択し、ファイル名とディレクトリを指定します。ファイル名は tb_test のように VHDL Module と異なる名前にしてください。

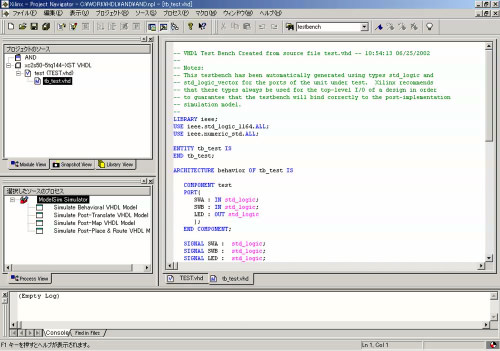

次のように、テストベンチの雛型が自動生成されます。

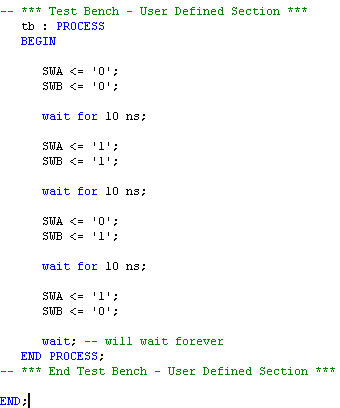

生成されたテストベンチの雛型にコードを追加します。修正するのはコメントで書かれた次の部分です。

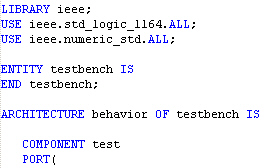

自動で生成されたテストベンチのエンティティ名は testbench となっています。必要に応じて変更してください。

5 シュミレーションの実行

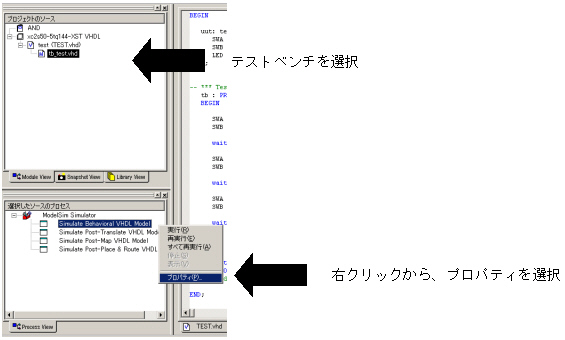

シミュレーションを行うための、オプション設定をします。次のようにプロパティを選択して下さい。

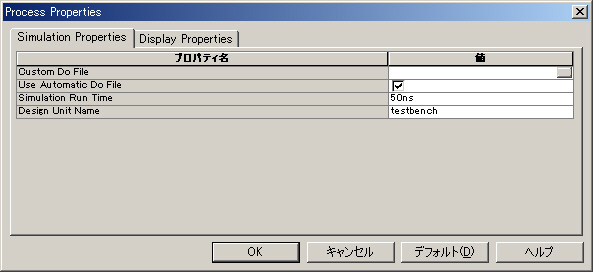

Simulation Run Time には実行時間 [ 50ns ] 、Design Unit Name にはテストベンチのエンティティ名を設定します。今回はエンティティ名がtestbenchのままなので、そのままにしておきます。

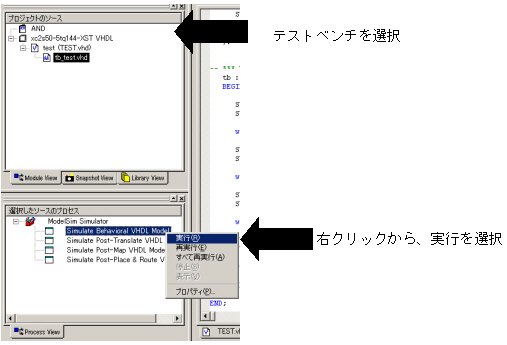

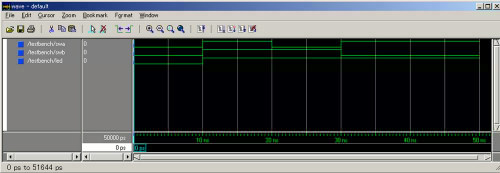

波形を確認します。ソースウィンドウの [ tb_test.vhd ] を選択し、プロセスウィンドウ [ Simulate Behavioral VHDL Module ] をダブルクリックするか、右クリックの[ 実行 ] を選択します。

Wave Windowにて波形を確認します。

6 ピン固定ファイルの作成

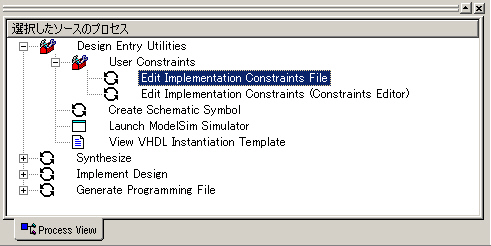

プロセスウィンドウの [ Design Entry Utilities ] → [ Edit Implement Constraints ] をダブルクリックします。

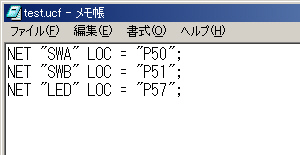

行の先頭に # を付けるとコメント文になります。SWA、SWB、LEDに対して、ピン配置を固定します。

7 論理合成と配置配線

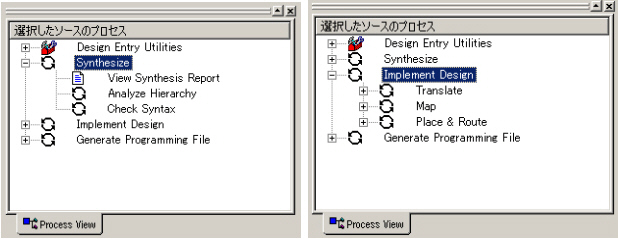

論理合成には [ Synthesize ] 、配置配線には [ Implement Design ] をダブルクリックします。

8 ビットファイルの作成

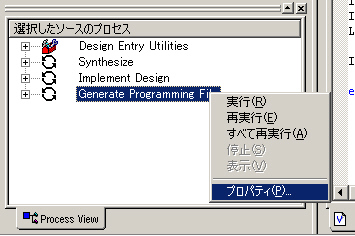

プロセスウィンドウの [ Generate Programming File ] のプロパティを選択します。

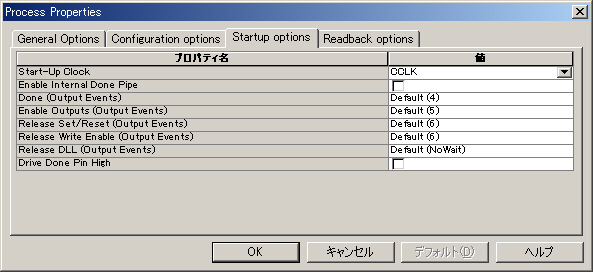

次のようなダイアログボックスが表示され、[ Startup options ] タブを選択します。一番上の [ Start-Up Clock ] はスレーブシリアルでコンフィグレーションするので、[CCLK] とします。

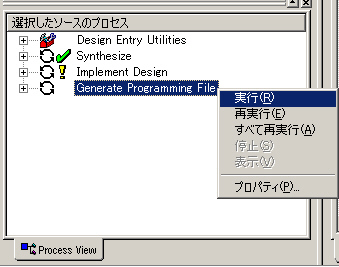

プロセスウィンドウの [ Generate Programming File ] を実行します。

ビットファイルはプロジェクトディレクトリ内にできます。今回は新規プロジェクトで指定した C:\WORK\HDL\AND\test.bit として作成されました。階層構造ではトップモジュール名がファイル名となります。