USB通信によるFPGA初期化方法

2002/10/18-

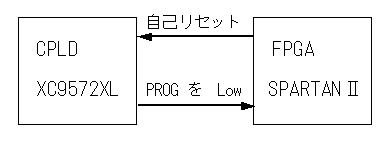

下図のように,FPGAが出力するリセット信号をCPLDが受け取り,PROGをLOWに下げ,FPGAを初期化する単純なものです.

FPGAがリセット信号を出力するということは,FPGA内部にある条件がきたら,リセットを出すという回路を記述する必要があります.例えば,USBから0x2Aを検出したら,1時間経過したら,などです.ピン番号はFPGAとCPLDで次の通りです.

| FPGA | L<0> : 96番 | L<1> : 95番 |

| CPLD | L<0> : 32番 | L<1> : 31番 |

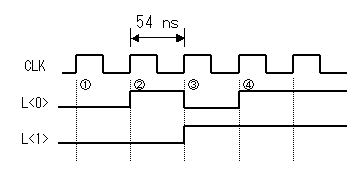

この2つのピンを使用して,下のタイムチャートのように L[1:0] を 00,01,10,11 でリセットをかけるようにCPLD内部回路を変更しました.今回は,2つの信号を考慮しましたが,1つの信号だけでも,リセットは可能です.

FPGAがこのように,カウントアップするとCPLDはリセット (PROGをLow) とします.このように自己リセットを加えた CPLD(XC9572XL) の回路は,次からダウンロードして下さい.

| CPLD内部回路/自己リセット対応 | ASB_CONF_RST.zip |

| JED ファイルのみ | ASB_CONF_RST.jed |

次に,エコー回路を例に,FPGAの内部回路について説明します.ここでは,USBから*(0x2A)が送られるとリセットさせます.この 0x2A とリードイネーブル信号にて,順に 00,01,10,11 を L [1:0] に出力されます.

SELF_RST port map ( CLK => CLK18M, RST => gd, ENB => ENB, DATA => DATA, L => L );

when S0 => L <= "00"; if( ENB='1' and DATA=X"2A") then STATE <= S1; end if; when S1 => L <= "01"; STATE <= S2; when S2 => L <= "10"; STATE <= S3; when S3 => L <= "11"; STATE <= S0; |

■USB通信によるエコー回路 ( 自己リセットを付加 )

| ISE プロジェクト | |

| VHDL | ASB004_12.zip |