2007/03/14-

VCCD_PLLはVCCINTに接続されるのがスタンダードで、ACM-014ではそうなっていないのはスタンダードではないことになります。

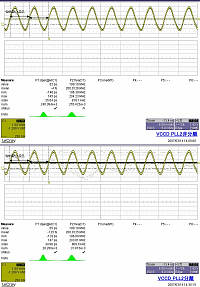

実際にこのことが、PLLの動作にどの様に影響するのか、ACM-014上の30MHzクロックより、PLL機能により200MHzを生成、オシロスコープのジッタ計測機能で比較してみました。

| 代表値 サイクル・トゥ・サイクル・ジッタ |

VCCD_PLLと VCCA_PLLを接続 |

VCCD_PLLと VCCA_PLLを分離 |

| ジッタ | 52[ps] | 55[ps] |

| ジッタ最大 | 145[ps] | 175[ps] |

なお、AMC-014の次回製造時よりVCCD_PLLとVCCA_PLLは分離されます。(Rev2となります)

波形をクロックして拡大

波形をクロックして拡大