乮娙堈側儘僕傾僫愙懕偵傕偛拲堄乯

2009/10/22-

偨偲偊偽丄壓婰偼FT2232H偺Sync-FIFO儌乕僪帪偺僋儘僢僋乮60MHz)偱偡偑丄FPGA偺INPUT懁傪娤應偡傞偲偛棗偺捠傝偱偡偑丄FPGA偼偳偆姶偠偰偄傞偺偱偟傚偆偐丅

丂FPGA偑擖椡偟偨怣崋傪FPGA偺暿偺僺儞偐傜弌椡偡傞偲椙偔傢偐傝傑偡丅

僋儕僢僋偟偰奼戝

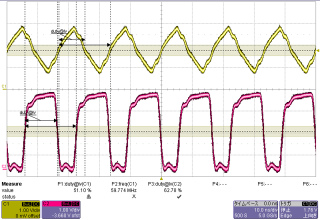

忋丗FPGA傊偺擖椡僺儞

壓丗FPGA偐傜偺弌椡

乮幚尡偑僶儔僢僋偱攝慄挿傕挿偄偨傔丄擖椡攇宍傕傂偢傫偱偄傑偡乯

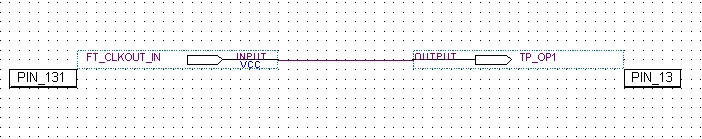

FPGA撪晹夞楬

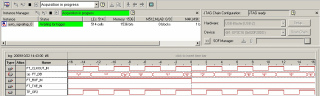

偲偙傠偱偙偺幚尡偵偼傕偆堦偮僆僠偑偁傝傑偡丅幚偼丄擖椡偵偼娙堈側USB儘僕傾僫偑愙懕偝傟偰偄偨偺偱偡丅

壓婰偵USB儘僕傾僫傪奜偟偨攇宍傪偍帵偟偟傑偡丅

僋儕僢僋偟偰奼戝

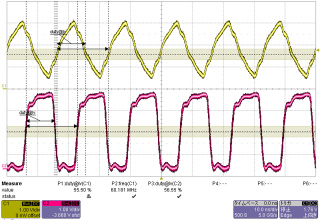

忋丗FPGA傊偺擖椡僺儞

壓丗FPGA偐傜偺弌椡

儘僕僢僋傾僫儔僀僓梡偵FPGA偺弌椡僺儞傪妱傝晅偗偰偍偄偰丄FPGA撪晹夞楬偱愙懕偡傟偽丄怣崋傪棎偡偙偲傕柍偔丄偮側偓懼偊傕昁梫側偄偺偱曋棙偱偡丅

乮壓婰偺僞僀儈儞僌偼偱偨傜傔偱偡乯

僋儕僢僋偟偰奼戝

偙偪傜偼丄FPGA撪晹偱丄擖椡乮60MHz)偐傜惗惉偟偨240MHz僋儘僢僋偱僒儞僾儕儞僌偟偨傕偺偱偡丅

USB儘僕傾僫傪愙懕偟偰娤應帪偵偼堘偭偨僨乕僞偵側偭偰偄傑偡丅