2002/04/12-

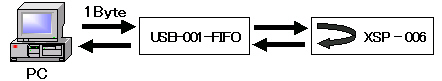

USBを用いた設計例として、USBの調停回路について紹介します。実験にはUSB-001-FIFOとXSP-006シリーズを用い、下の図のようにFPGA内部に実装したUSB制御回路を介してデータをエコーします。この回路を利用することに制限はありませんが、ご使用にはお客さまの責任でお願いします。使用した結果について弊社は一切関知いたしません。

▼実験の概略図

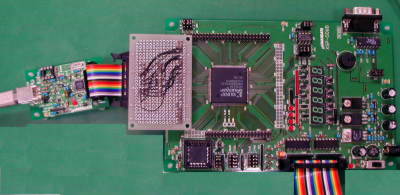

USB-001-FIFOとXSP-006には下の写真のように手配腺で接続しました。通信ソフトから1ByteのデータをUSB-001-FIFOに送信し、そのデータをXSP-006のFPGAが受信します。FPGAは受信したデータをそのまま返信します。このFPGA内部回路として記述したVHDLソースを公開します。

▼実験の写真 |

| USB-001-FIFO | XSP-006 | |

| D0 | 3 | 70 |

| D1 | 4 | 71 |

| D2 | 5 | 69 |

| D3 | 6 | 68 |

| D4 | 7 | 63 |

| D5 | 8 | 67 |

| D6 | 9 | 61 |

| D7 | 10 | 62 |

| RD# | 11 | 60 |

| WR | 12 | 59 |

| TXE# | 13 | 58 |

| RXF# | 14 | 57 |

上表のように配線した場合のUCFファイルは例えば以下のようになります。

▼UCFファイル

NET "CLK" LOC = "P80" ;

NET "USB_DATA<0>" LOC = "P70";

NET "USB_DATA<1>" LOC = "P71";

NET "USB_DATA<2>" LOC = "P69";

NET "USB_DATA<3>" LOC = "P68";

NET "USB_DATA<4>" LOC = "P63";

NET "USB_DATA<5>" LOC = "P67";

NET "USB_DATA<6>" LOC = "P61";

NET "USB_DATA<7>" LOC = "P62";

NET "RD" LOC = "P60";

NET "RXF" LOC = "P57";

NET "WR" LOC = "P59";

NET "TXE" LOC = "P58";

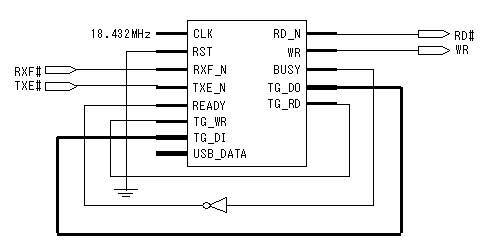

使用する際には、回路図かHDLエディタにて、USB_ARBITER.vhdを以下のように結線してください。この回路についての詳しい解説もございます。

▼VHDLソース

USB_ARBITER.vhd

▼上位の回路図

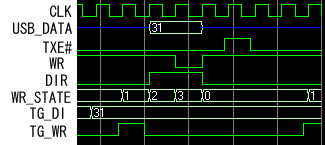

USBからの読込みはRXF#、書込みにはTXE#の状態を調べ、お互いに重ならないように調停を行います。詳しいタイミングはデータシート等を見てください。書込みと読込みのステートマシンを別に作成します。

▼書込み時

State0 : TG_WRの立ち上がりで、TG_DIを取り込む

State1 : (Read State)読込み中でなければ、DIR=1(バスの方向を変える)

State2 : WR=0、 DIR=1(バスの方向を維持)

State3 : WR=1に戻し、DIR=0(バスの方向をFPGA側に戻す)

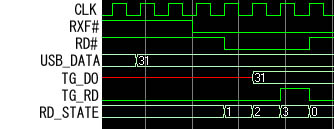

State0 : RXF#の立ち下がりで、RD#=0にする

State1 : USB_DATAを取り込む

State2 : TG_RD=1にする

State3 : TG_RD=0に戻す