スパルタン ブレッドボード XSP-008-150/200 ユーザーズマニュアル 初版(R2)

# 目次

| はじめに                |

|---------------------|

| ご注意                 |

| 1. 製品の内容について        |

| 2.各部の名称             |

| 2.1. 電源入力           |

| 2.2. JTAG コネクタ      |

| 3.ジャンパスイッチの説明       |

| 4. XSP-008 参考資料について |

| 5. 付属資料             |

## はじめに

この度は、スパルタン ブレッドボード / XSP-008 をお買い上げいただきまして誠にありがとうございます。

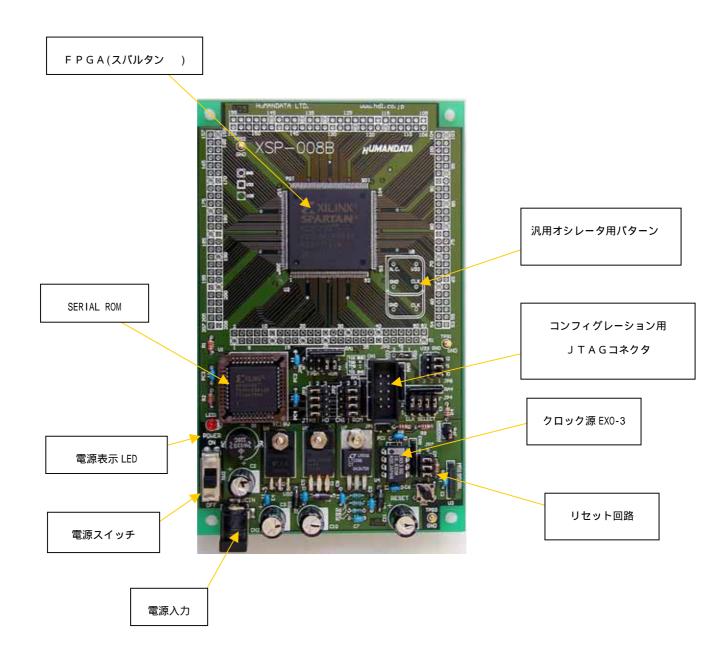

XSP-008 は、ザイリンクスの高性能 FPGA スパルタン (XC2S)を用いた評価用ボードで、電源回路、リセット回路、クロック回路、コンフィグレーション回路、ISP 可能なコンフィグレーション ROM などを装備した使いやすいボードになっています。

どうぞご活用ください。

### ご注意

- 1. 本書の内容は、改良のため将来予告なしに変更することがありますので、ご了承願います。

- 2. 本書の内容については万全の記して作成しましたが、万一誤りなど、お気づきの点がございましたら、ご連絡をお願いいたします。

- 3. 本製品の運用の結果につきましては、2.項にかかわらず当社は責任を負いかねますので、ご了承願います。

- 4. 本書に記載されている使用と異なる使用をされ、あるいは本書に記載されていない使用をされた場合の結果については、当社は責任を負いません。

- 5. 本書および、回路図、サンプル回路などを無断で複写、引用、配布することはお断りいたします。

## 1.製品の内容について

本パッケージには、以下のものが含まれています。万一、不足などがございましたら、弊社宛にご連絡ください。

| FPGAブレッドボード/XSP-008 | 1 |

|---------------------|---|

| 付属品(予備ジャンパなど)       | 1 |

| AC アダプタ             | 1 |

| マニュアル ( 本書 )        | 1 |

| ユーザー登録はがき           | 1 |

## 2.各部の名称

## 2.1. 電源入力

本ボードは、DC9V単一電源で動作します。

内部で必要な、5V、3.3V、2.5V はオンボードのレギュレータにより生成されます。

内部でブリッジダイオードを使用しているため、電源ジャックに極性はありません。

2.1 の標準的なACアダプタ(9から12V)を用いることができます。

付属の AC アダプタをご使用ください。

## 2.2. JTAG コネクタ

F P G A へのコンフィグレーション、 ISP 可能なシリアル ROM への書込みに用います。 ピン配置は次表のとおりです。

| 信号名 | ピン番号 | ピン番号 | 信号名 |

|-----|------|------|-----|

| TCK | 1    | 2    | GND |

| TDO | 3    | 4    | VCC |

| TMS | 5    | 6    | -   |

| -   | 7    | 9    | -   |

| TDI | 9    | 10   | GND |

弊社製ダウンロードケーブルХС2、ХСКІТの10ピンコネクタと1:1で対応しています。

シリアルROMによりコンフィグレーションする場合は、内蔵の XC18V02PC44C に JTAG 経由で ISP(オンボード書込み) してください。

オンボードで、シリアルROMに ISP するときは、ジャンパ設定で、JTAG チェインに ROM を接続してください。

## 3. ジャンパスイッチの説明

## JP4 クロック選択(次表を参照ください)

| ピン番号 | クロック名         | BAS 側        | DIV 側         |

|------|---------------|--------------|---------------|

| 1-2  | FPGA の GCLOKO | EX0-03 基本周波数 | EXO-03 の分周出力。 |

| 3-4  | FPGA の GCLOK1 | 18.432MHz    | JP7 で設定。      |

| 5-6  | FPGA の GCLOK2 |              |               |

| 7-8  | FPGA の GCLOK3 |              |               |

### J P7 DIV 側クロック設定 (次表を参照ください)

EXO-03(クロック発生器 1 8 . 4 3 2 M H z )

| ,     | ,     |       |           |

|-------|-------|-------|-----------|

| J P7  |       |       |           |

| 1-2 間 | 2-3間  | 4-5間  | 周波数       |

| SHORT | SHORT | SHORT | 9.216 MHz |

| OPEN  | SHORT | SHORT | 4.608 MHz |

| SHORT | OPEN  | SHORT | 2.304 MHz |

| OPEN  | OPEN  | SHORT | 1152 KHz  |

| SHORT | SHORT | OPEN  | 576 KHz   |

| OPEN  | SHORT | OPEN  | 288 KHz   |

| SHORT | OPEN  | OPEN  | 144 KHz   |

| OPEN  | OPEN  | OPEN  | 72 KHz    |

#### JP8 M0, M2 信号処理用(回路図参照)

出荷時:Master Serial mode

JP8 1-2 間ショート MO=L

JP8 4-5 間ショート M1=L

JP8 7-8 間ショート M2=L

#### JP6 リセット回路無効/有効切り替え

ショートで、 パワーオンリセット回路およびリセットボタンが有効です。

(出荷時はショート)

#### JP3 コンフィグレーションモード設定

JTAG 側で、 JTAG モードとなります。

HD 側でハードウエアデバッガモードとなります。

ハードウエアデバッガモード時には ROM と併用できませんので必ず ROM を取外しておいてください。

(出荷時は JTAG 側)

### JP2 コンフィグレーションソース設定

ROM 側で ROM からのコンフィグレーションとなります。

CN1 側で、ケーブルからのコンフィグレーションとなります。

これは、ハードウエアデバッガモード時の設定です。

通常は ROM 側でかまいません。 (JTAG)

(出荷時は ROM 側)

#### JP5 JTAG チェイン切り替え

|           | 1-2 間、3-4 間<br>ショート          | 5-6間、7-8間<br>ショート |

|-----------|------------------------------|-------------------|

| JTAG チェイン | JTAG にはコンフィグレーション<br>ROM が接続 | JTAG には FPGA が接続  |

## 4. XSP-008 参考資料について

追加資料や参考資料がつくられた場合は

製品サポートページ

http://www.hdl.co.jp/support\_c.html にデータをアップロードすることにいたします。

拡張子".exe"のときは、自己解凍ファイルといたします。

ときどきチェックしていただき必要に応じてご利用くださいませ。

パスワードを求められたときは"thanks"を入力していただければ開けます。

## 5. 付属資料

1 . 基板回路図

## スパルタン2ブレッドボード

XSP-008-150/200

ユーザーズマニュアル

2001/09/29 初版(R2)

## 有限会社ヒューマンデータ

〒567-0034

大阪府茨木市中穂積1-2-51

シャトー春日第3ビル

TEL 072-620-2002

FAX 072-620-2003

URL http://www.hdl.co.jp/

Mail support@hdl.co.jp