A P E X プレッドボード C S P - 0 2 2 シリーズ Rev 2 ユーザーズマニュアル

有限会社ヒューマンデータ 第3版

# 目次

| はじめに                                  | 2   |

|---------------------------------------|-----|

| ご注意                                   | 2   |

| 製品の内容について                             | 3   |

| ボード概観                                 | 4   |

| 電源入力                                  | 5   |

| 汎用 LED                                | 5   |

| クロック用ジャンパの説明                          | 6   |

| VCC10 を外部より供給する方法                     | 7   |

| コンフィグレーション方法                          | 8   |

| PSモードによるコンフィグレーション方法                  | 8   |

| QUALTUS から CSP-021 上の EPC2 に ISP する方法 | .10 |

| コンパイル時の設定                             | .10 |

| EPC2 への書込み方法                          | .11 |

| JTAG <b>経由のコンフィグレーション方法</b>           | .12 |

| 付属資料                                  | .12 |

### はじめに

この度は、APEX ブレッドボードをお買い上げいただきまして誠にありがとうございます。 CSP-022シリーズはアルテラ社の高性能 FPGA である APEX シリーズを実装した試作 評価用ボードで、リセット回路、クロック源、電源回路などの必要最低限の機能に絞り、全 ピンを拡張コネクタに引き出した使いやすいボードになっています。 どうぞご活用ください。

#### ご注意

- 1. 本書の内容は、改良のため将来予告なしに変更することがありますので、ご了承願います。

- 2. 本書の内容については万全の記して作成しましたが、万一誤りなど、お気づきの点が ございましたら、ご連絡をお願いいたします。

- 3. 本製品の運用の結果につきましては、2.項にかかわらず当社は責任を負いかねますので、ご了承願います。

- 4. 本書に記載されている使用と異なる使用をされ、あるいは本書に記載されていない使用をされた場合の結果については、当社は責任を負いません。

- Quartus、MAX+Plus、APEX は、米国アルテラ社の商標です。

### 製品の内容について

本パッケージには、以下のものが含まれています。万一、不足などがございましたら、弊社 宛にご連絡ください。

| APEX プレッドボード    | 1 |

|-----------------|---|

| A C アダプタ ( 6 V) | 1 |

| ジャンパ、ヘッダピンセット   | 1 |

| マニュアル (本書)      | 1 |

| ユーザー登録カード       | 1 |

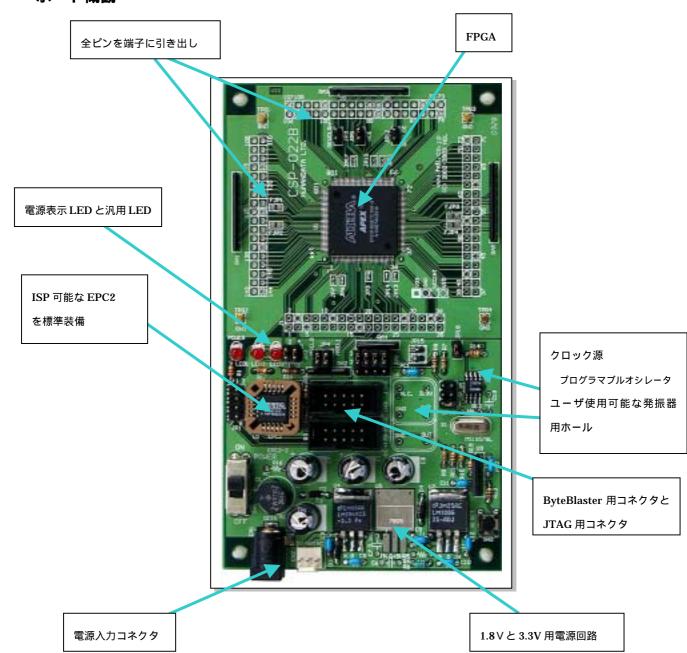

# ボード概観

注)写真は、CSP-022-160Eです。モデルにより多少の差違がございます。

### 電源入力

付属の AC アダプタ(6 V)を用いる場合は、CN1 に接続します。 CN2 より、DC 5 V を供給することも可能です。

AC アダプタに極性はありません。

#### CN2

| ピン番号 | 信号名 |

|------|-----|

| 1    | +5V |

| 2    | GND |

| 3    | N.C |

# 汎用 LED

汎用 LED 2 個が FPGA から点灯できます。 それぞれ、切り離し用JPにより取り外すことができます。 汎用 LED は FPGA の出力を L とすることで点灯します。

| ピン番号 | 信号名  | 切離し用 JP    |

|------|------|------------|

| 2    | LED2 | JP2(1-2 間) |

| 3    | LED3 | JP2(3-4 間) |

# クロック用ジャンパの説明

### JP8 クロック選択

| ショート位置 | クロック         | ショート位置 | クロック       |

|--------|--------------|--------|------------|

| ピン番号   |              | ピン番号   |            |

| 2-3    | FPGA の 95pin | 1-2    | オプションの汎    |

| 5-6    | FPGA の 23pin | 4-5    | 用発振器(XCO)よ |

| 8-9    | FPGA の 92pin | 7-8    | IJ         |

| 11-12  | FPGA の 20pin | 10-11  |            |

# JP18、JP16 クロック周波数設定

CY2071AF(クロック発生器:原発クリスタル 16.00MHz)

| JP18=オープン  |       |       |       |          |  |

|------------|-------|-------|-------|----------|--|

| JP16:いずれかシ | 1-2 間 | 3-4 間 | 5-6間  | 周波数      |  |

| ョート        | SHORT | -     | -     | 80 MHz   |  |

| (同時ショート禁   | -     | SHORT | -     | 40 MHz   |  |

| 止)         | -     | -     | SHORT | 20 MHz   |  |

| JP18=ショート  |       |       |       |          |  |

| JP16:いずれかシ | SHORT | -     | -     | 66MHz    |  |

| ョート        |       |       |       | 出荷時      |  |

| (同時ショート禁   | -     | SHORT | -     | 33MHz    |  |

| 止)         | -     | -     | SHORT | 16.5 MHz |  |

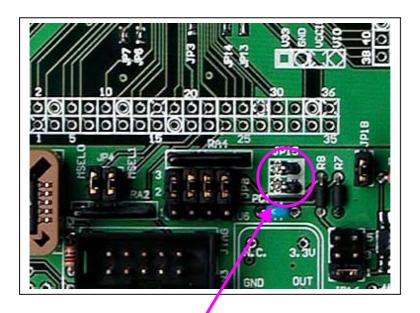

# VCCIO を外部より供給する方法

JP15 を 2 本ともカットすると、外部より VCCIO が供 給できます。

### コンフィグレーション方法

CSP-022 では、3つのコンフィグレーション方法があります。

- ByteBlasterMV などによるアルテラ独自方式:PSモード (パッシブシリアル)

- 2. JTAG による方法 (ByteBlasterMV などを用いる) :JTAG

- 3. コンフィグレーション ROM (内蔵 EPC2)による:ROM

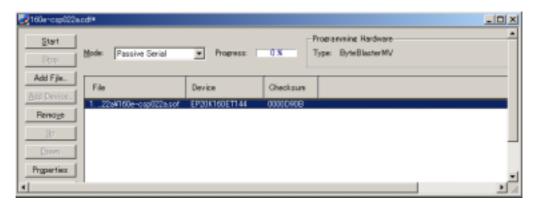

### PSモードによるコンフィグレーション方法

PS モードでコンフィグレーションするには、ボード上の JP1 を 4 個すべて取り外し、オンボードの EPC2 を切り離してください。

(EPC2 が実装されていなければ、JP30 はショートでかまいません) また、ダウンロードケーブルは、CN1(CONFIG)へ接続します。 以下に、コンパイルから、コンフィグレーションまでの手順を示します。

1 ) ターゲットに合ったデバイスを固定してコンパイルしてください。

**2)** Programmer の Mode で PassiveSerial を選択してください。 AddFile により、pof ファイルを設定します。

**3)** ByteBlasterMV (弊社の BLKIT または BL2 も同様)をターゲットの PS-MODE (パッシブシリアル)用コネクタ(CN4)に接続し、Start のボタンをクリックすれば、コンフィグレーションが完了します。

つぎに、EPC2 への書込み方法と、JTAG でのコンフィグレーション方法を説明いたします。

### Qualtus から CSP-021 上の EPC2 に ISP する方法

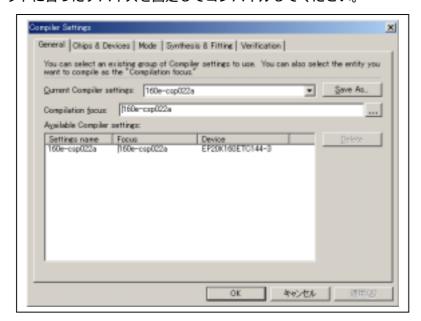

### コンパイル時の設定

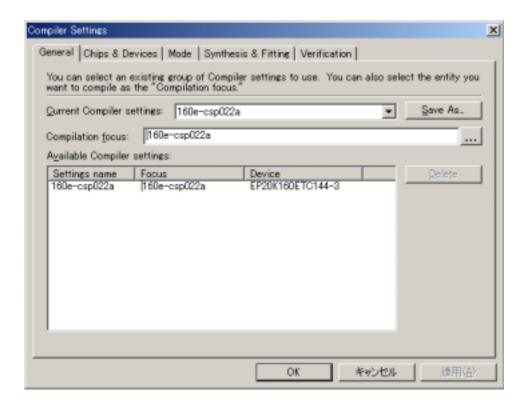

Compiler Settings の Chip & Devices のタブで図のように設定してください。

Use Configration EPROMを"EPC2"に設定してください。

### EPC2 への書込み方法

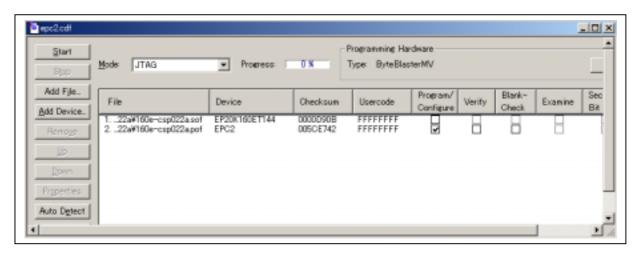

EPC2 への書込みは JTAG により行います。 JTAG ではダウンロードケーブルを JTAG(CN3)のコネクタに接続します。

JTAG チェーンには、EPC2 と APEX がつながっています。それらの状態を、Qualtus の JTAG Cain Setup により設定します。図を参考に設定してください。

ファイルの並びは、1:EPF20K 2:EPC2の順です。

このとき、APEXには書込みをしないので、チェックをはずしておきます。

# JTAG 経由のコンフィグレーション方法

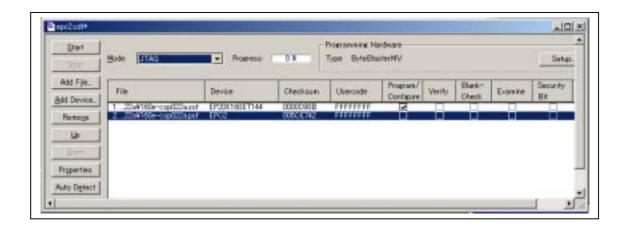

JTAG 経由でコンフィグレーションするには下図のように、EPC2 へのプログラムのチェックを外し、APEX へのチェックを加えます。

# 付属資料

1.回路図

APEX ブレッドボード CSP-022 シリーズ Rev 2

# ユーザーズマニュアル

2002/6/18 Rev1 初版 2003/04/03 Rev1 第2版 2003/07/29 Rev2 第3版

# 有限会社ヒューマンデータ

〒567-0034

大阪府茨木市中穂積1-2-51

シャトー春日第3ビル

TEL 072-620-2002

FAX 072-620-2003

URL http://www.hdl.co.jp

Mail support@hdl.co.jp