# HUMANDATA

## Cyclone ブレッドボード ACM-014 シリーズ ユーザーズマニュアル 第3版(Rev2)

ヒューマンデータ

### 目次

| はじめに                     | 1  |

|--------------------------|----|

| ご注意                      | 1  |

| 1. 製品の内容について             | 2  |

| 2. 仕様                    | 2  |

| 3. 各部の名称                 | 3  |

| 3.1. 電源入力                | 4  |

| 3.2. JTAG コネクタ           | 4  |

| 3.3. AS コネクタ             | 5  |

| 3.4. SIO 用コネクタ           | 5  |

| 3.5. ジャンパスイッチの説明         | 6  |

| 3.6 RAM 切り離し方法           | 7  |

| 4. ピン割付表                 | 7  |

| 4.1. ユーザ I/O CNA         | 7  |

| 4.2. ユーザ I/O CNB         | 8  |

| 4.3. FLASH-ROM           | 8  |

| 4.4. SRAM                | 9  |

| 4.5. 汎用 LED              | 9  |

| 4.6. 汎用スイッチ              | 9  |

| 4.7 SIO 用                | 9  |

| 5. 固定ピンについて              | 10 |

| 6. ACM-014 シリーズ 参考資料について | 11 |

| 7. 付属資料                  | 11 |

#### はじめに

この度は、Cyclone ブレッドボード / ACM-014 シリーズをお買い上げいただきまして誠にありがとうございます。 ACM-014 シリーズは、アルテラ社の高性能 FPGA である Cyclone を用いた評価用ボードで、電源回路、リセット回路、クロック回路、コンフィグレーション回路、ISP 可能なコンフィグレーション ROM などを装備した使いやすいボードになっています。

どうぞご活用ください。

#### ご注意

- 1. 本書の内容は、改良のため将来予告なしに変更することがありますので、ご了承願います。

- 2. 本書の内容については万全の記して作成しましたが、万一誤りなど、お気づきの点がございましたら、ご連絡をお願いいたします。

- 3. 本製品の運用の結果につきましては、2.項にかかわらず当社は責任を負いかねますので、ご了承願います。

- 4. 本書に記載されている使用と異なる使用をされ、あるいは本書に記載されていない使用をされた場合の結果については、当社は責任を負いません。

- 5. 本書および、回路図、サンプル回路などを無断で複写、引用、配布することはお断りいたします。

### 1. 製品の内容について

本パッケージには、以下のものが含まれています。万一、不足などがございましたら、弊社宛にご連絡ください。

| FPGA ブレッドボード | ACM-014 シリーズ | 1 |

|--------------|--------------|---|

| 付属品          |              | 1 |

| マニュアル(本書)    |              | 1 |

| ユーザー登録はがき    |              | 1 |

### 2. 仕様

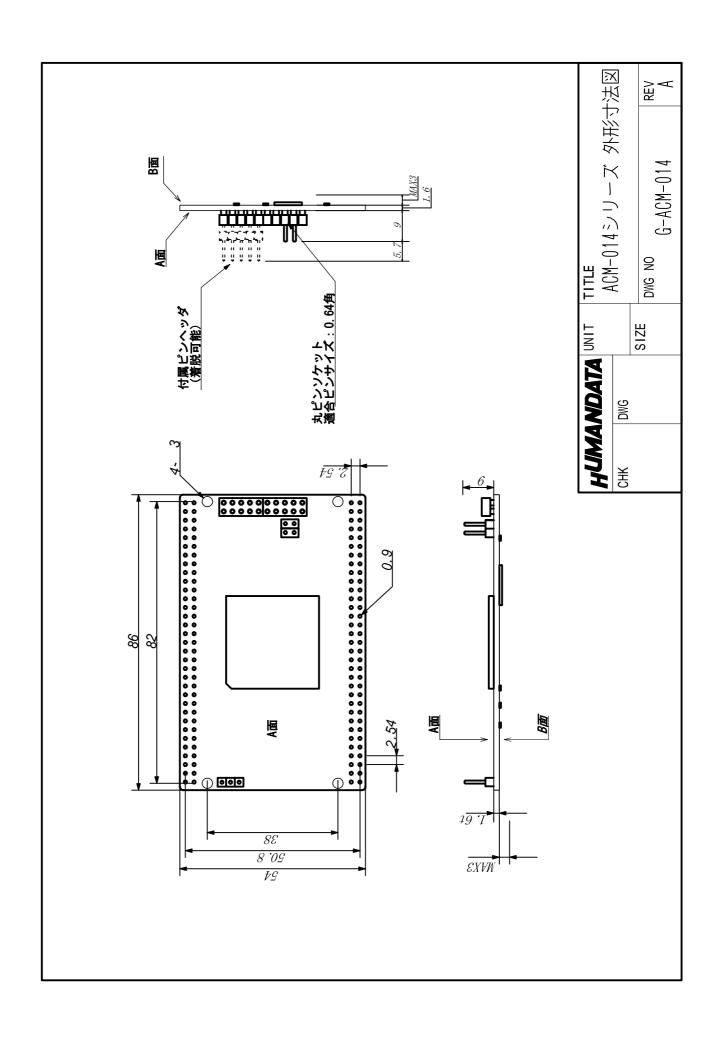

| 製品型番           | ACM-014-5                    | ACM-014-8   |  |  |  |

|----------------|------------------------------|-------------|--|--|--|

| 搭載 FPGA        | EP2C5Q208C8                  | EP2C8Q208C8 |  |  |  |

| 電源             | DC 3.3V (内部電源はオンボードレ         | ギュレータにより生成) |  |  |  |

| 消費電流           | N/A (詳細は FPGA データシートご        | 参照)         |  |  |  |

| 外形寸法           | 86 × 54 [mm]                 |             |  |  |  |

| 重量             | 約 28 [g]                     |             |  |  |  |

| ユーザ 1/0        | 100 本 (一部 RAM アドレスと共         | 用)          |  |  |  |

| プリント基板         | ガラスエポキシ 4 層基板 1.6t           |             |  |  |  |

| コンフィグレーション ROM | EPCS4 (ALTERA)               |             |  |  |  |

| SRAM           | CY62256VLL-70ZC (CYPRESS) *1 |             |  |  |  |

| シリアル FLASH-ROM | M25P40-VMN6P (ST) *1         |             |  |  |  |

| クロック           | オンボード 30MHz 外部供給可能           |             |  |  |  |

| リセット回路         | 内蔵 (240ms TYP)               |             |  |  |  |

| JTAG コネクタ      | DIP10 ピン 丸ピンソケット 2.54mn      | n ピッチ       |  |  |  |

| AS コネクタ        | DIP10 ピン 丸ピンソケット 2.54mn      | n ピッチ       |  |  |  |

| ステータス LED      | 2個 (POWER-LED , CONF_DON     | IE-LED)     |  |  |  |

| 汎用 LED         | 1 個                          |             |  |  |  |

| 汎用タクトスイッチ      | 1個                           |             |  |  |  |

|                | DIP10 ピンヘッダ(本体に取付け済る         | み) 1 個      |  |  |  |

| 付属品            | ヘッダ 2x40 2本                  |             |  |  |  |

|                | ジャンパソケット 2個                  |             |  |  |  |

<sup>\*1</sup> 互換品に変更されることがあります

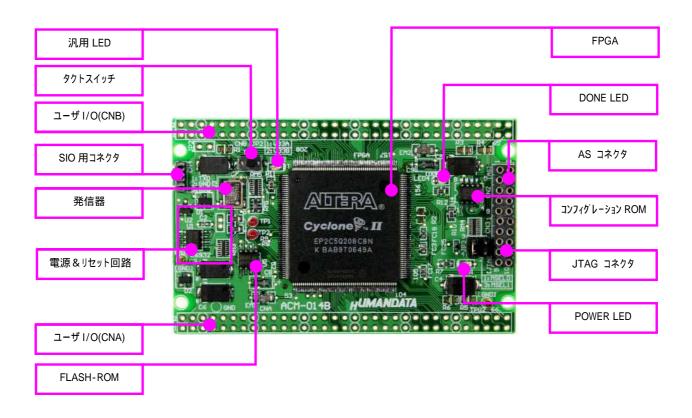

#### 3. 各部の名称

3

### 3.1. 電源入力

本ボードは、DC 3.3V単一電源で動作します。

外部から供給する 3.3V 電源は充分安定して、充分な余裕のあるものをご用意ください。 電源は CNA、CNB から供給してください。

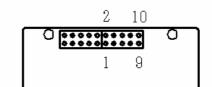

### 3.2. JTAG コネクタ

FPGA へのコンフィグレーション時に使用します。 ピン配置は次表のとおりです。

CN3

| 回路図上信号名 | ダウンロードケーブル<br>信号名 | ピン番号 | ピン番号 | ダウンロードケーブル<br>信号名 | 回路図上信号名   |

|---------|-------------------|------|------|-------------------|-----------|

| XTCK    | TCK               | 1    | 2    | GND               | GND       |

| XTDO    | TDO               | 3    | 4    | VCC(3.3V)         | VCC(3.3V) |

| XTMS    | TMS               | 5    | 6    | -                 | -         |

| -       | -                 | 7    | 8    | -                 | -         |

| XTDI    | TDI               | 9    | 10   | GND               | GND       |

弊社製ダウンロードケーブルB L 3、 B L K I T の 1 0 ピンコネクタと 1 : 1 で対応しています。 ALTERA 社の純正ケーブルを用いることもできます。

また、ダウンロードロードケーブルと本品との接続には付属品 DIP10 ピンヘッダをご利用できます

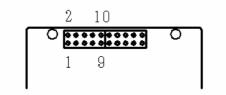

#### 3.3. AS コネクタ

コンフィグレーション ROM(EPCS)への ISP

(In System Programming) 時に使用します。

ピン配置は次表のとおりです。

CN2

| 回路図上信号名   | ダウンロードケーブル<br>信号名 | ピン番号 | ピン番号 | ダウンロードケーブル<br>信号名 | 回路頭上信号名   |

|-----------|-------------------|------|------|-------------------|-----------|

| XDCLK     | DCLK              | 1    | 2    | GND               | GND       |

| XCONFDONE | CONF_DONE         | 3    | 4    | VCC(3.3V)         | VCC(3.3V) |

| XNCONFIG  | nCONFIG           | 5    | 6    | nCE               | nCE       |

| XDATAO    | DATAOUT           | 7    | 8    | nCS               | nCS       |

| X_ASDO    | ASDI              | 9    | 10   | GND               | GND       |

弊社製ダウンロードケーブルBL3、BLKITの10ピンコネクタと1:1で対応しています。 ALTERA 社の純正ケーブルを用いることもできます。

また、ダウンロードロードケーブルと本品との接続には付属品 DIP10 ピンヘッダをご利用できます

#### 3.4. SIO 用コネクタ

CN4

| 信号名 | コネクタピン# | FPGA ピン# |

|-----|---------|----------|

| TXD | 1       | 41       |

| GND | 2       |          |

| RXD | 3       | 43       |

SIO 用コネクタは、FPGA の出力をそのまま接続してあります。 SIO として以外に、汎用入出力として使用する事も出来ます。

#### 3.5. ジャンパスイッチの説明

| <b>Configuration Scheme</b>  | MSEL1 | MSELO |

|------------------------------|-------|-------|

| AS (20 MHz)                  | 0     | 0     |

| PS                           | 0     | 1     |

| Fast AS (40 MHz)             | 1     | 0     |

| JTAG-based Configuration (1) | (2)   | (2)   |

- (1) JTAG-based configuration takes precedence over other configuration schemes, which means MSEL pin settings are ignored.

- (2) Do not leave the MSEL pins floating; connect them to  $V_{\text{CCIO}}$  or ground. These pins support the non-JTAG configuration scheme used in production. If you are only using JTAG configuration, you should connect the MSEL pins to ground. (ALTERA 社データシートより)

MSELO, MSEL1 信号 設定用 JP3

| JP3 | MSEL  |

|-----|-------|

| 1-2 | MSEL0 |

| 3-4 | MSEL1 |

ROM 使用時: JP3 (1-2間:ショート 3-4 間:ショート)

MSELO = 0

MDEL1 = 0

JTAG 使用時(出荷時): JP3 (1-2間:オープン 3-4 間:ショート)

MSEL0 = 1

MDEL1 = 0

注:本来はどのモードでも JTAG 経由のコンフィグレーションは可能ですが、ROM の内容が不定 (BLANK 含む) の時には、AS モードでのコンフィグレーションが動作中のため、PS モードにすることで安定したコンフィグ レーションが可能です。

### 3.6 RAM 切り離し方法

RAM が不要のとき、ハンダ面 PTJP(回路図参照)でカットすることで切り離しが可能です。

### 4. ピン割付表

### 4.1. ユーザ I/O CNA

| 備考      | NET LABEL | デバイス pin # | コネクタ | タ pin # | デバイス pin # | NET LABEL | 備考      |

|---------|-----------|------------|------|---------|------------|-----------|---------|

| 電源      | VIN3      | 3.3V       | 1    | 2       | 3.3V       | VIN3      | 電源      |

| 5V 電源予約 | VIN5      | 5V         | 3    | 4       | 5V         | VIN5      | 5V 電源予約 |

|         | GND       | GND        | 5    | 6       | GND        | GND       |         |

|         | IOA0      | 3          | 7    | 8       | 4          | IOA1      |         |

| Α       | IOA2      | 5          | 9    | 10      | 6          | IOA3      | Α       |

| ^       | IOA4      | 8          | 11   | 12      | 10         | IOA5      | Α       |

|         | IOA6      | 11         | 13   | 14      | 12         | IOA7      |         |

|         | GND       | GND        | 15   | 16      | GND        | GND       |         |

|         | IOA8      | 13         | 17   | 18      | 14         | IOA9      |         |

| В       | IOA10     | 15         | 19   | 20      | 30         | IOA11     | В       |

|         | IOA12     | 31         | 21   | 22      | 33         | IOA13     | Ь       |

|         | IOA14     | 34         | 23   | 24      | 35         | IOA15     |         |

|         | GND       | GND        | 25   | 26      | GND        | GND       |         |

|         | IOA16     | 37         | 27   | 28      | 39         | IOA17     |         |

| С       | IOA18     | 40         | 29   | 30      | 68         | IOA19     | С       |

| C       | IOA20     | 69         | 31   | 32      | 70         | IOA21     |         |

|         | IOA22     | 72         | 33   | 34      | 74         | IOA23     |         |

|         | GND       | GND        | 35   | 36      | GND        | GND       |         |

|         | IOA24     | 75         | 37   | 38      | 76         | IOA25     |         |

| D       | IOA26     | 77         | 39   | 40      | 80         | IOA27     | D       |

| Б       | IOA28     | 81         | 41   | 42      | 82         | IOA29     | Б       |

|         | IOA30     | 84         | 43   | 44      | 86         | IOA31     |         |

|         | GND       | GND        | 45   | 46      | GND        | GND       |         |

|         | IOA32     | 87         | 47   | 48      | 88         | IOA33     |         |

| Е       | IOA34     | 89         | 49   | 50      | 90         | IOA35     | Е       |

| _       | IOA36     | 92         | 51   | 52      | 94         | IOA37     | _       |

|         | IOA38     | 95         | 53   | 54      | 96         | IOA39     |         |

|         | GND       | GND        | 55   | 56      | GND        | GND       |         |

|         | IOA40     | 97         | 57   | 58      | 99         | IOA41     |         |

|         | IOA42     | 101        | 59   | 60      | 102        | IOA43     |         |

| F       | IOA44     | 103        | 61   | 62      | 105        | IOA45     | F       |

|         | IOA46     | 106        | 63   | 64      | 107        | IOA47     |         |

|         | IOA48     | 108        | 65   | 66      | 110        | IOA49     |         |

### 4.2. ユーザ I/O CNB

| 備考      | NET LABEL | デバイス pin #          | コネクケ  | タ pin # | デバイス pin # | NET LABEL | 備考      |

|---------|-----------|---------------------|-------|---------|------------|-----------|---------|

| 電源      | VIN3      | 3.3V                | 1     | 2       | 3.3V       | VIN3      | 電源      |

| 5V 電源予約 | VIN5      | 5V                  | 3     | 4       | 5V         | VIN5      | 5V 電源予約 |

|         | GND       | GND                 | 5     | 6       | GND        | GND       |         |

|         | IOB0      | 208                 | 7     | 8       | 207        | IOB1      |         |

| Α       | IOB2      | 206                 | 9     | 10      | 205        | IOB3      | Α       |

|         | IOB4      | 203                 | 11    | 12      | 201        | IOB5      |         |

|         | IOB6      | 200                 | 13    | 14      | 199        | IOB7      |         |

|         | GND       | GND                 | 15    | 16      | GND        | GND       |         |

|         | IOB8      | 198                 | 17    | 18      | 197        | IOB9      |         |

| В       | IOB10     | 195                 | 19    | 20      | 193        | IOB11     | В       |

|         | IOB12     | 192                 | 21    | 22      | 191        | IOB13     | , b     |

|         | IOB14     | 189                 | 23    | 24      | 188        | IOB15     |         |

|         | GND       | GND                 | 25    | 26      | GND        | GND       |         |

|         | IOB16     | 187                 | 27    | 28      | 185        | IOB17     |         |

| С       | IOB18     | 182                 | 29    | 30      | 181        | IOB19     | С       |

|         | IOB20     | IOB20 180 31 32 179 | IOB21 | · ·     |            |           |         |

|         | IOB22     | 176                 | 33    | 34      | 175        | IOB23     |         |

|         | GND       | GND                 | 35    | 36      | GND        | GND       |         |

|         | IOB24     | 173                 | 37    | 38      | 171        | IOB25     |         |

| D       | IOB26     | 170                 | 39    | 40      | 169        | IOB27     | D       |

|         | IOB28     | 168                 | 41    | 42      | 165        | IOB29     |         |

|         | IOB30     | 164                 | 43    | 44      | 163        | IOB31     |         |

|         | GND       | GND                 | 45    | 46      | GND        | GND       |         |

|         | IOB32     | 162                 | 47    | 48      | 161        | IOB33     |         |

| Е       | IOB34     | 160                 | 49    | 50      | 152        | IOB35     | Е       |

| _       | IOB36     | 151                 | 51    | 52      | 150        | IOB37     | _       |

|         | IOB38     | 149                 | 53    | 54      | 147        | IOB39     |         |

|         | GND       | GND                 | 55    | 56      | GND        | GND       |         |

|         | IOB40     | 146                 | 57    | 58      | 145        | IOB41     |         |

|         | IOB42     | 144                 | 59    | 60      | 143        | IOB43     |         |

| F       | RAMA9     | 118                 | 61    | 62      | 117        | RAMA10    | F       |

|         | RAMA11    | 113                 | 63    | 64      | 112        | RAMA12    |         |

|         | RAMA13    | 114                 | 65    | 66      | 115        | RAMA14    |         |

部分は RAM アドレスと共用

### 4.3. FLASH-ROM

M25P40-VMN6P

| FLASH-ROM ピン# | NET LABEL | FPGA ピン# |

|---------------|-----------|----------|

| U5-1          | SPI_CS    | 46       |

| U5-2          | SPI_SI    | 47       |

| U5-6          | SPI_CK    | 44       |

| U5-5          | SPI_SO    | 45       |

8

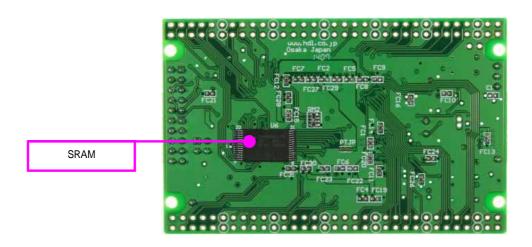

### 4.4. SRAM

#### CY62256VLL-70Z

| SRAM ピン# | NET LABEL | FPGA<br>ピン# |

|----------|-----------|-------------|

| U6-1     | RAMA5     | 134         |

| U6-2     | RAMA6     | 133         |

| U6-3     | RAMA7     | 128         |

| U6-4     | RAMA8     | 127         |

| U6-5     | RAMA9     | 118         |

| U6-6     | RAMA10    | 117         |

| U6-7     | RAMA11    | 113         |

| U6-8     | RAMA12    | 112         |

| U6-9     | RAMA13    | 114         |

| U6-10    | RAMA14    | 115         |

| U6-11    | RAMD0     | 116         |

| U6-12    | RAMD1     | 67          |

| U6-13    | RAMD2     | 64          |

| U6-14    | GND       |             |

| SRAM ピン# | NET LABEL | FPGA<br>ピン# |

|----------|-----------|-------------|

| U6-15    | RAMD3     | 63          |

| U6-16    | RAMD4     | 61          |

| U6-17    | RAMD5     | 60          |

| U6-18    | RAMD6     | 59          |

| U6-19    | RAMD7     | 58          |

| U6-20    | RAMCEn    | 57          |

| U6-21    | RAMA0     | 56          |

| U6-22    | RAMOEn    | 142         |

| U6-23    | RAMA1     | 141         |

| U6-24    | RAMA2     | 139         |

| U6-25    | RAMA3     | 138         |

| U6-26    | RAMA4     | 137         |

| U6-27    | RAMWEn    | 135         |

| U6-28    | V33A      |             |

部分は I/O ピンにも出力されています。 (CNB)

### 4.5. **汎用** LED

| LED  | NET LABEL | FPGA<br>ピン# |

|------|-----------|-------------|

| LED2 | ULED0     | 48          |

### 4.6. 汎用スイッチ

| SW  | NET LABEL | FPGA<br>ピン# |

|-----|-----------|-------------|

| SW1 | SW0       | 104         |

### 4.7 SIO用

| CN4 | NET LABEL | FPGA<br>ピン# |

|-----|-----------|-------------|

| 1   | TXD       | 41          |

| 3   | RXD       | 43          |

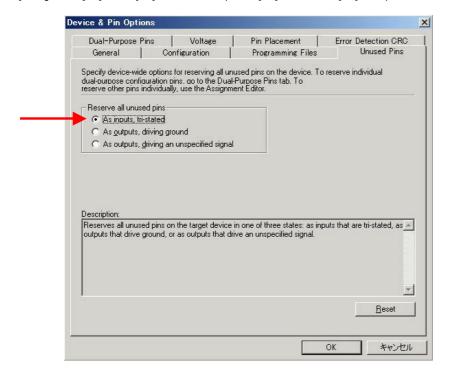

#### 5. 固定ピンについて

本ボードでは、下記のピンが GND または VCCINT(1.2V)に固定されています。

デバイスによっては、ダミー入力とし他に使わないようにする必要があります。

EP2C70 では GND や VCCINT になっているものの、より小さなデバイスでは 1/0 として割り付けられています。

#### 固定ピン一覧

GND

36,119

VCCINT

32,120

上記のダミー入力とする方法によらず未使用ピンを全て入力とすることもできます。

Quartus の Device Option により設定できます。

[Assignments] [Device] [Device & Pin Options] [Unused Pins] [As inputs,tri-stated]にチェック。

### 6. ACM-014 シリーズ 参考資料について

追加資料や参考資料がつくられた場合は

製品サポートページ

http://www.hdl.co.jp/support\_c.html

にデータをアップロードすることにいたします。

拡張子".exe"のときは、自己解凍ファイルといたします。

ときどきチェックしていただき必要に応じてご利用くださいませ。

#### 7. 付属資料

- 1 . 基板回路図

- 2 . 外形寸法図

### Cyclone ブレッドボード

ACM-014 シリーズ

### ユーザーズマニュアル

2005/11/11 初版 2006/05/26 初版(A) 2007/04/27 第 2版 (Rev2) 2007/06/21 第 3版 (Rev2)

### 有限会社ヒューマンデータ

〒567-0034

大阪府茨木市中穂積1-2-10

ジブラルタ生命茨木ビル

TEL 072-620-2002

FAX 072-620-2003

URL http://www.hdl.co.jp/