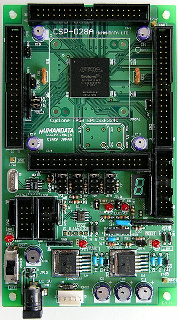

CSP-028シリーズ (FBGA324Pin)

2004/03/10-

※CSP-028にはディスコン部品がある為、受注生産もできません。

| Cyclone ブレッドボード CSP-028シリーズは、アルテラ社の高性能・低価格FPGAを実装した評価用基板の 完成品です。 FPGAの周辺3列分のI/OピンをGPIFコネクタに引き出してあります。 電源回路、リセット回路、クロック源、ISP可能コンフィグレーションROMを実装しています。 CSP-026シリーズから、引き出すIOピンを減らし、ボードを小型化してコストダウンいたしました。 Cycloneシリーズはアルテラ社の無料ツール(QuartusII web Edition)でサポートされています。 QuartusII web Editionサポートデバイス

|

アルテラサイトへジャンプ |

|

|

仕様

■FPGA

EP1C4F324、EP1C12F324またはEP1C20F324

機能 EP1C4F324 EP1C12F324 EP1C20F324 LE数 4,000 12,060 20,060 M4K RAMブロック数

(128X26ビット)12 52 64 トータルRAMビット数 78,336 239,616 294,912 PLL数 2 2 2 ■ASモード用コネクタ

ASモード時はByteBlasterII、USB Blasterまたは、弊社BL3またはBLKIT(REV2)が必要になります。

[2005/3/28:JICファイルにより、JTAG経由でEPCSに書込む方法]

PSモードには対応しておりません。

■JTAG用コネクタ

BL3、BLKIT(REV2)、ByteBlasterMV、ByteBlasterII、USB Blasterなどのダウンロードケーブル対応

■クロック源

Cypress: CY2071A: 80MHz,66MHz,40MHz,33MHz,20MHz,16.5MHzからジャンパで選択可能。/CY2071Aの設定

周波数設定ジャンパ

オプションの汎用クリスタルオシレータ実装用パターン。

■コンフィグレーションROM

EPCS4(10000回以上の書き換え可能)

EPCS4への書込みにはByteBlasterIIまたは、弊社BL3、BLKIT(REV2)が必要になります。

■リセット回路

リセットIC:M51957BL

■ステータスLED

CONF_DONE用、INIT_DONE用、POWER LED、POWER GOOD(3.3V-A,3.3V-B,1.5V)

ユーザ使用7セグメントLED:1桁(ソケット実装で切り離し可能)

■電源回路

5V入力から3.3V、1.5Vを生成。

VCCIOを2系統に分離。

■6層基板採用

■基板寸法:85mm X 147mm

| 品名 | MODEL | 実装FPGA | 税込標準価格 | 購入 | サポート |

| Cyclone FBGA324pin ブレッドボード | CSP-028-4C8 | EP1C4F324C8 | お問合せ | ||

| Cyclone FBGA324pin ブレッドボード | CSP-028-12C8 | EP1C12F324C8 | |||

| Cyclone FBGA324pin ブレッドボード | CSP-028-20C8 | EP1C20F324C8 |

※CSP-028にはディスコン部品がある為、受注生産もできません。

実験用ACアダプタ